ELEC211-FOR EXAM

ELEC211 notes

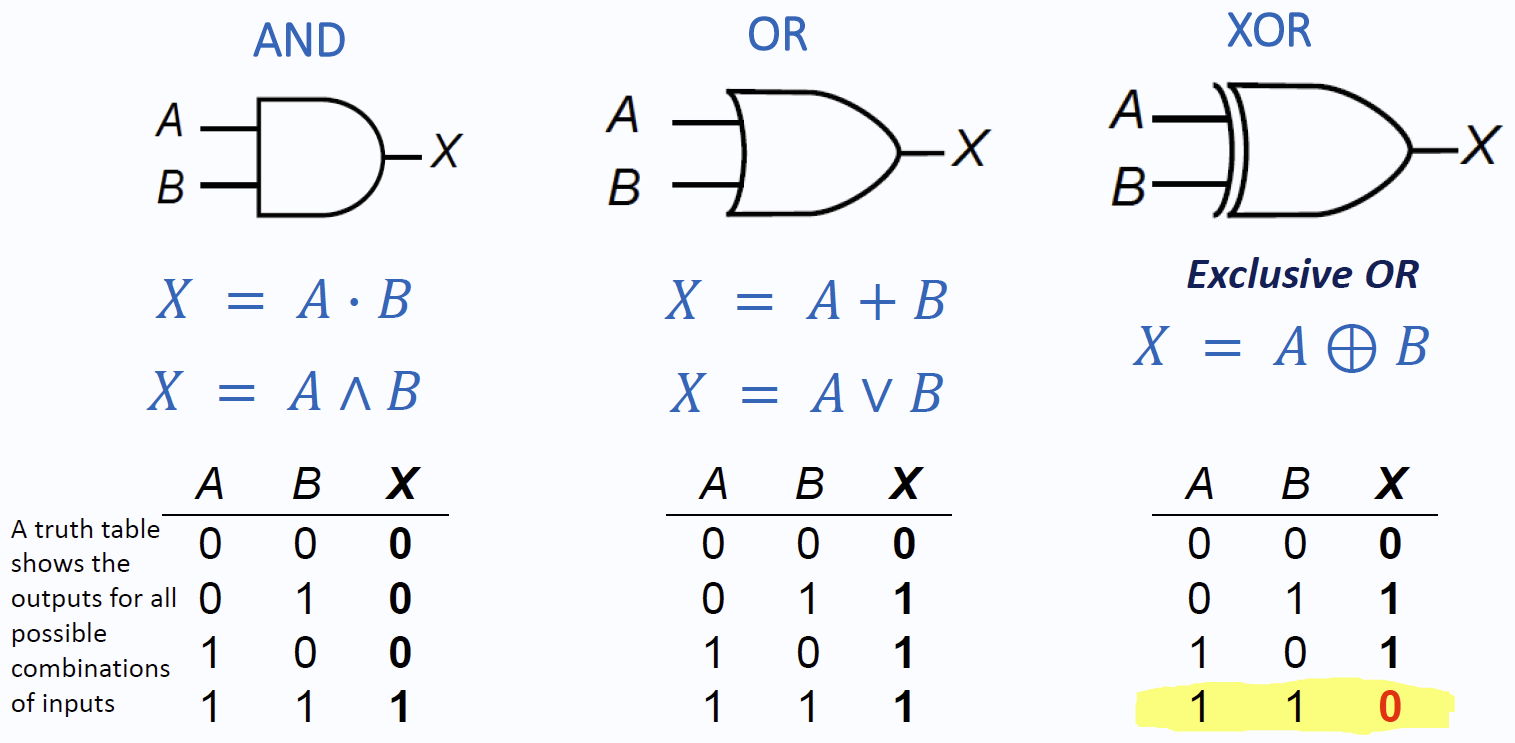

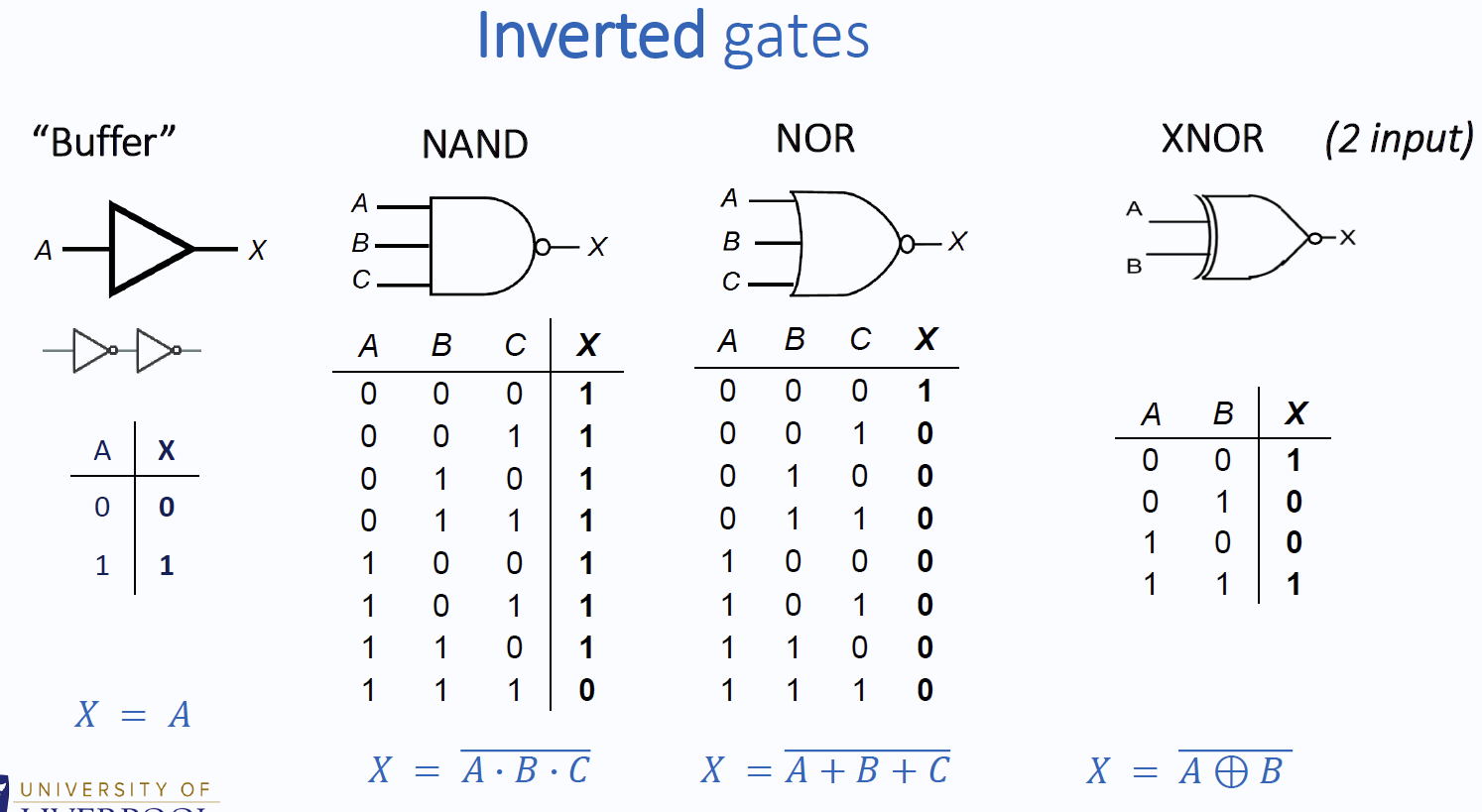

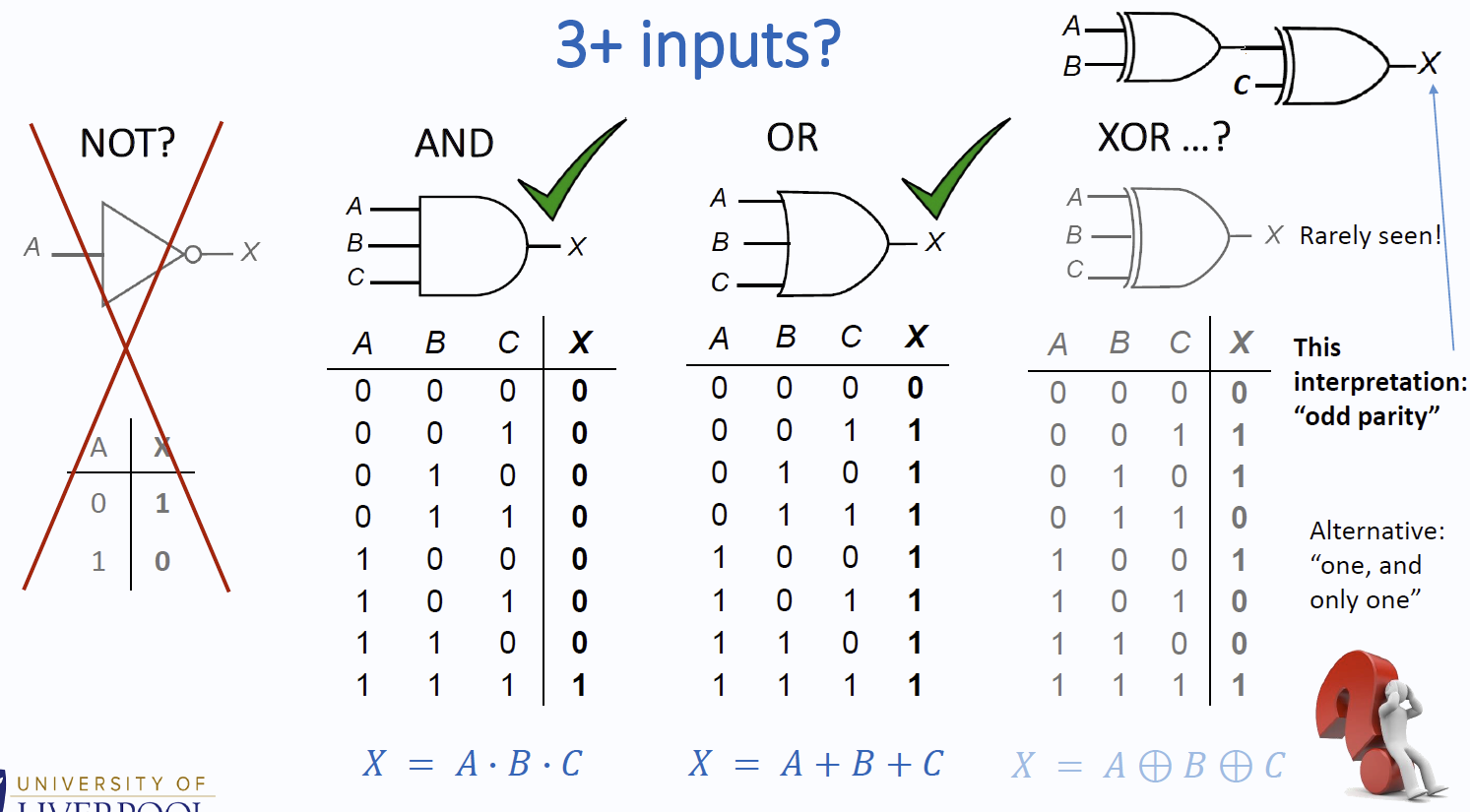

Logic gates and combinational logic

其中,NAND 和 NOR 也被称为Universal gates,因为我们可以仅使用他们中的某一种来实现所有的布尔逻辑

此处XOR逻辑=“取奇数输入”,少见。X = ((A XOR B) XOR C)

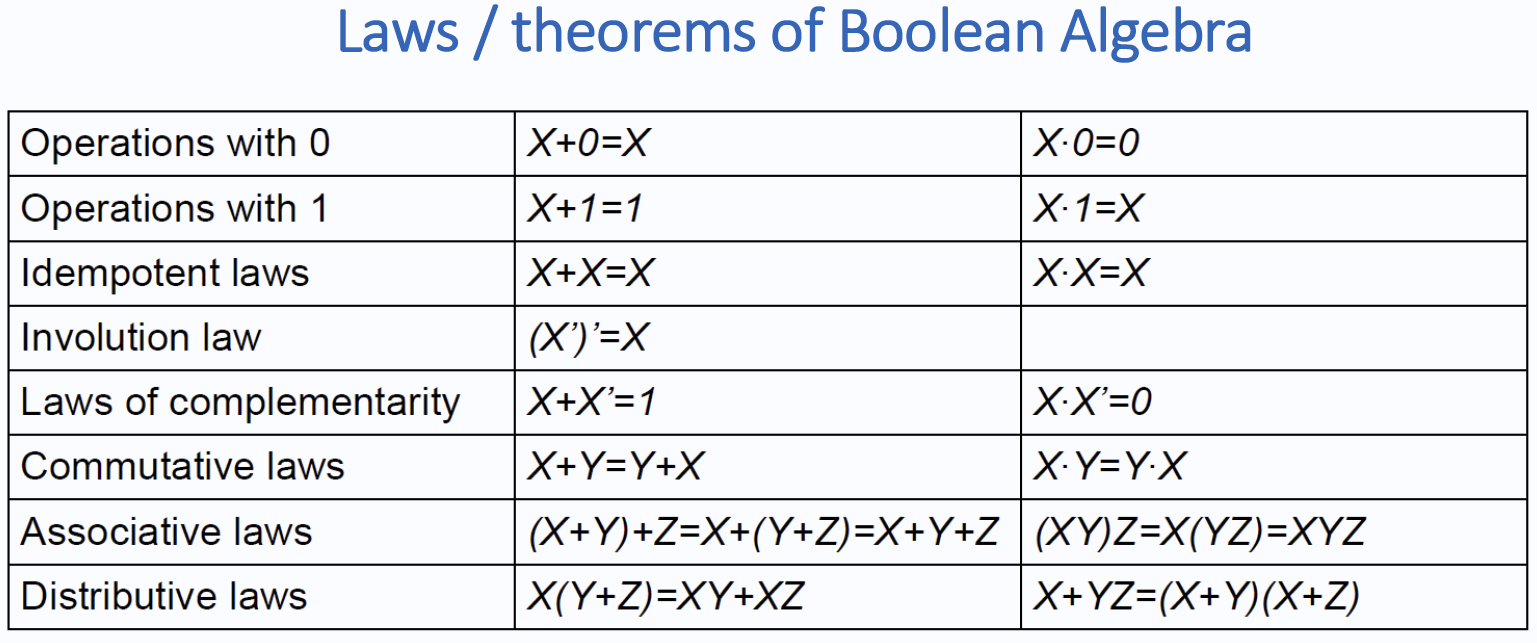

Combinational circuits 组合电路 •Present output depends only on present input •Combinational logic uses Boolean algebra:

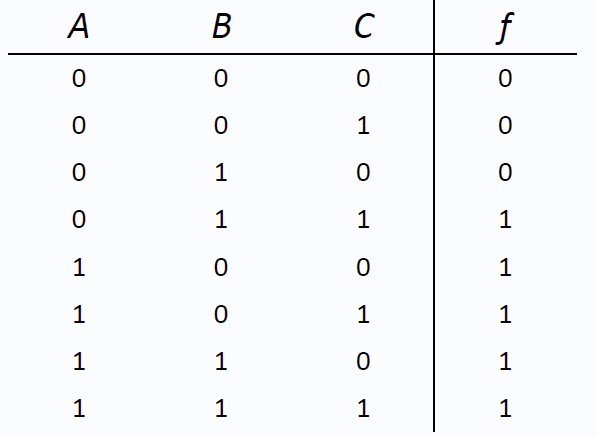

*使用卡诺图化简通常比看这种表格来得更快。

Sequential circuits 时序电路 •Present output values depend on present and past values •Circuit ‘remembers’ its own state

Minterms/Maxterms and implementing functions

Minterms: Sum of Products (SOP)

Maxterms: Product of Sums (POS)`

implementing

functions: 大概就是这个意思,不如卡诺图。

大概就是这个意思,不如卡诺图。

Karnaugh maps

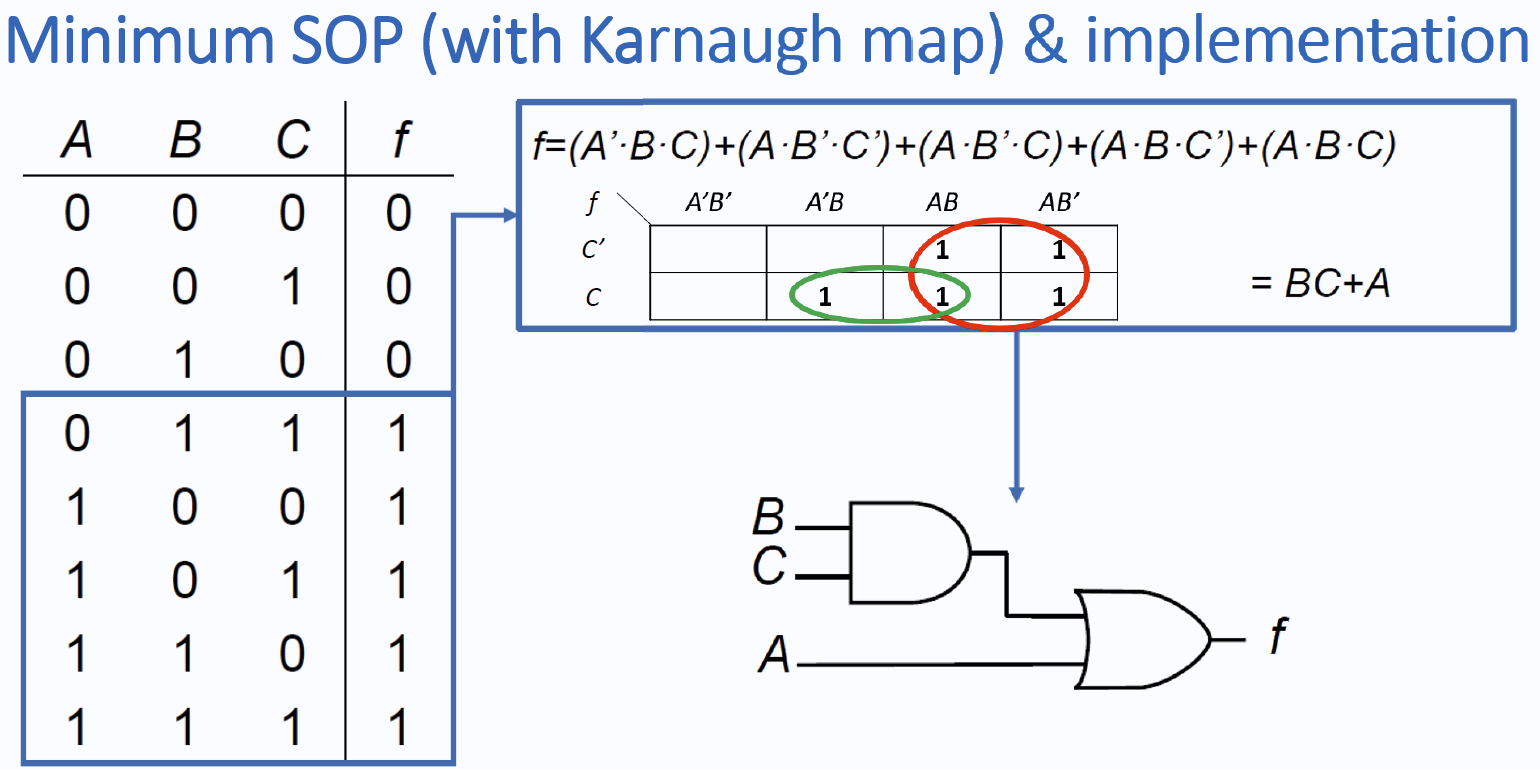

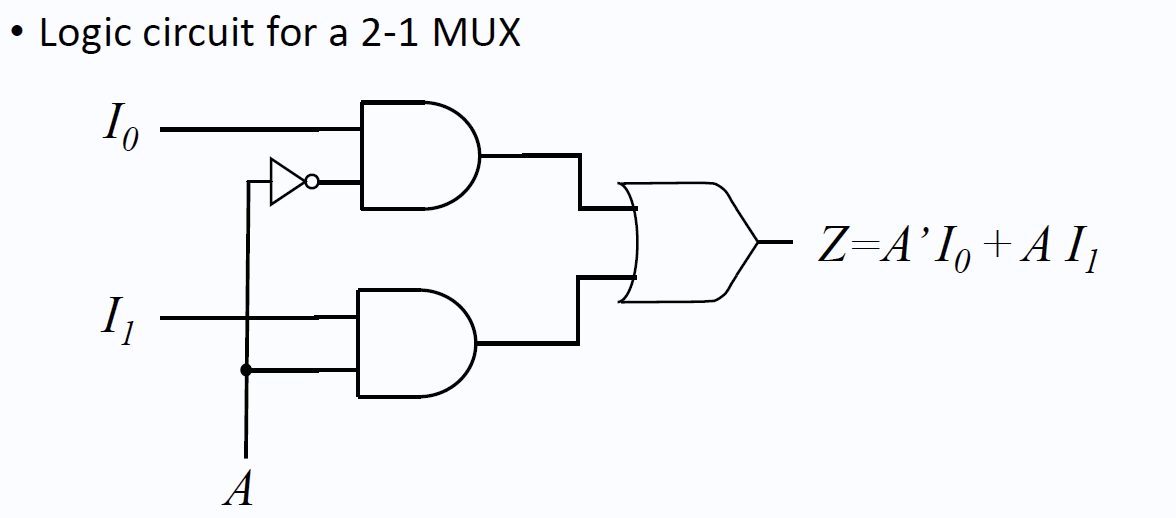

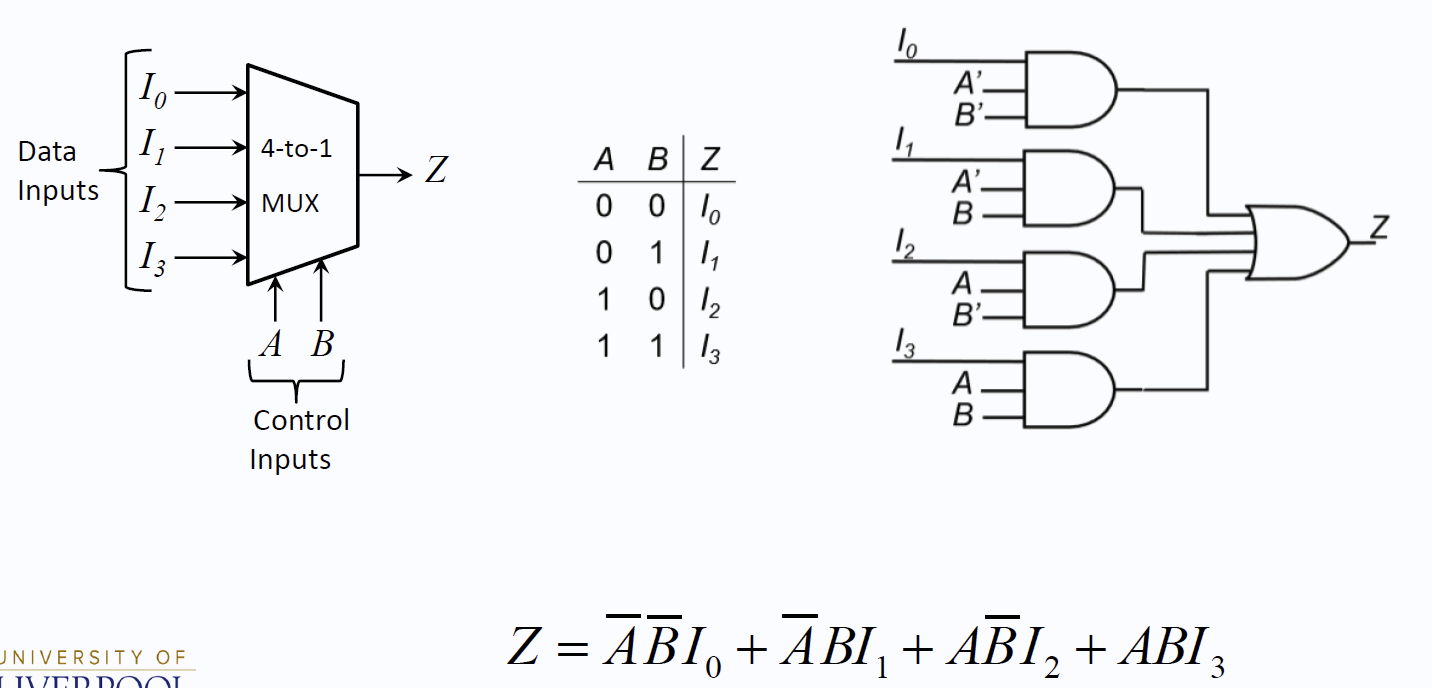

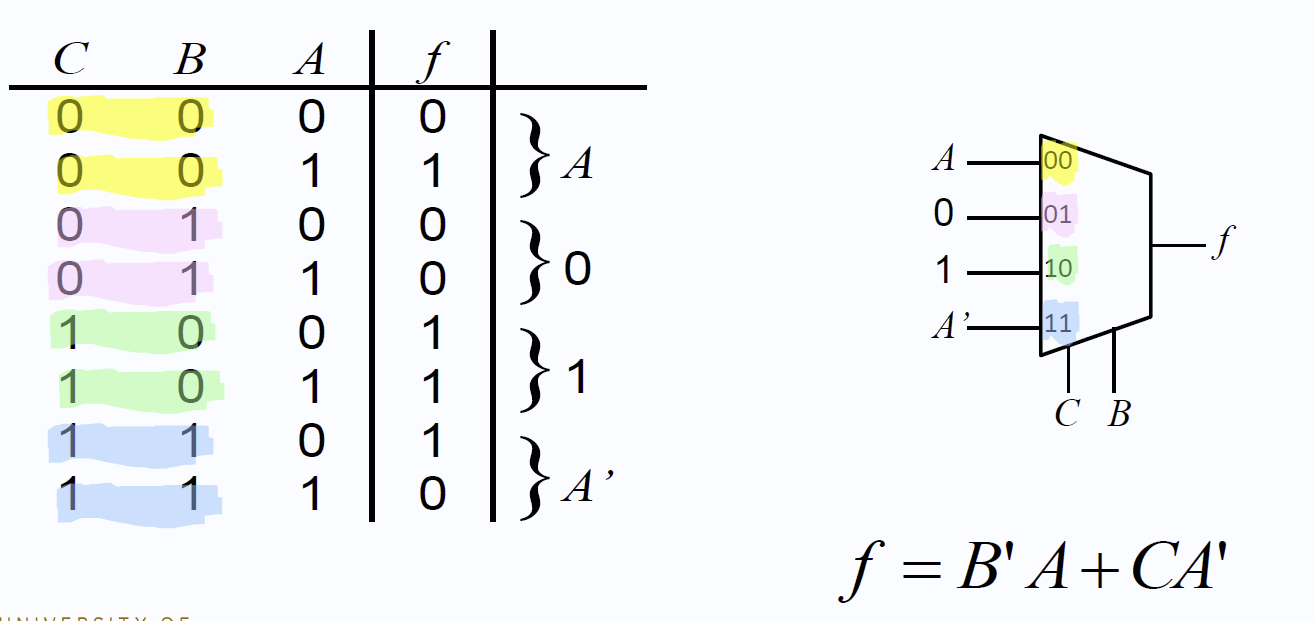

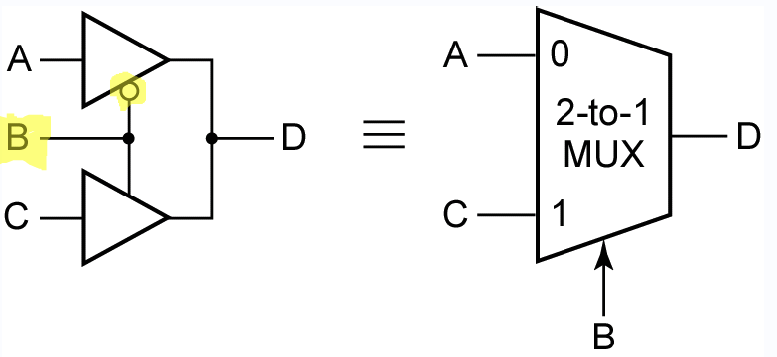

Multiplexer 数据选择器/多路开关

A multiplexer在多个输入中,依据数个控制用输入(control inputs)选择一个作为输出。(下图右)

A multiplexer has: •At least two inputs •One or more control (select) inputs •One output

实现:

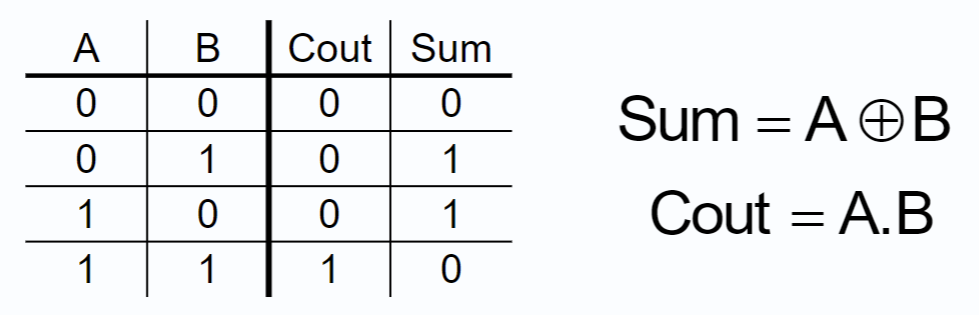

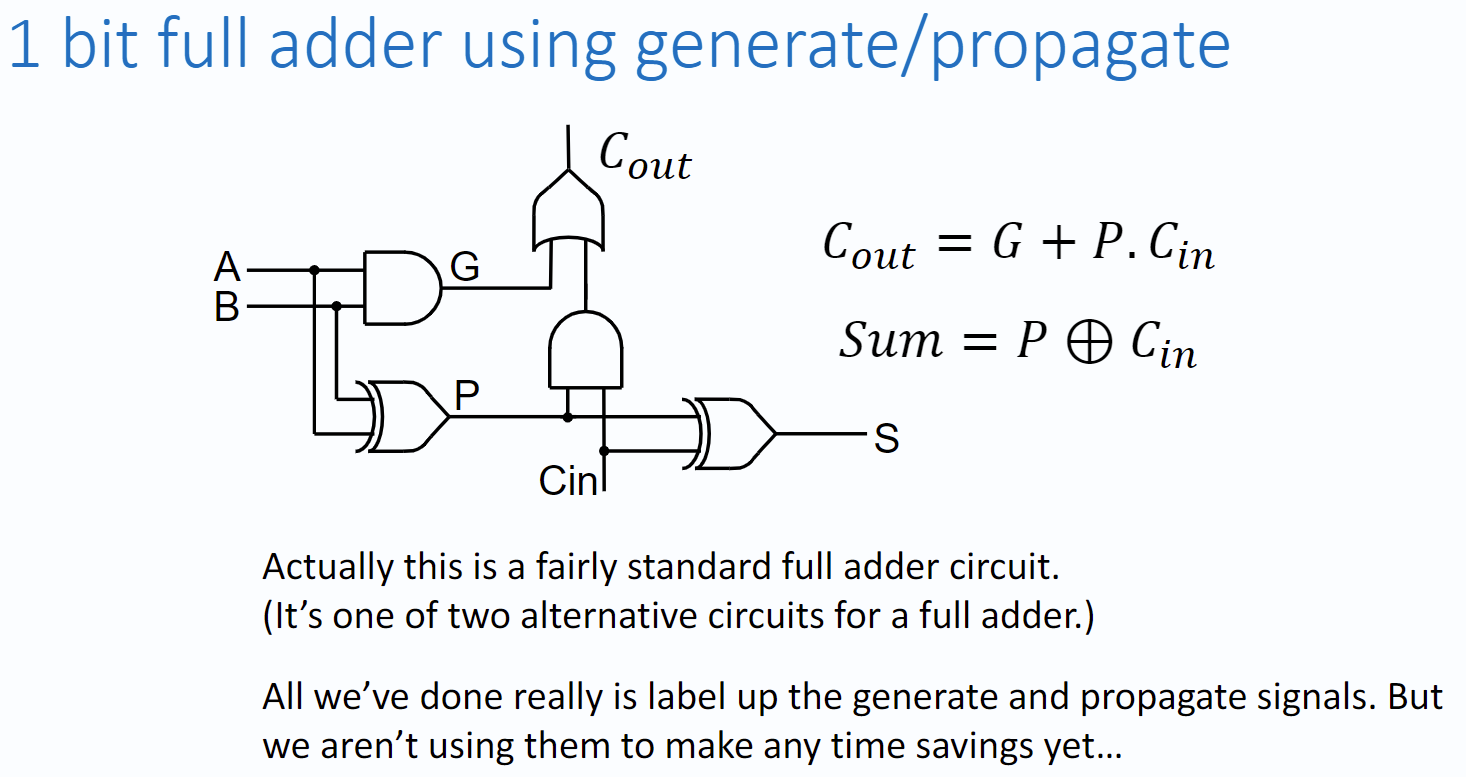

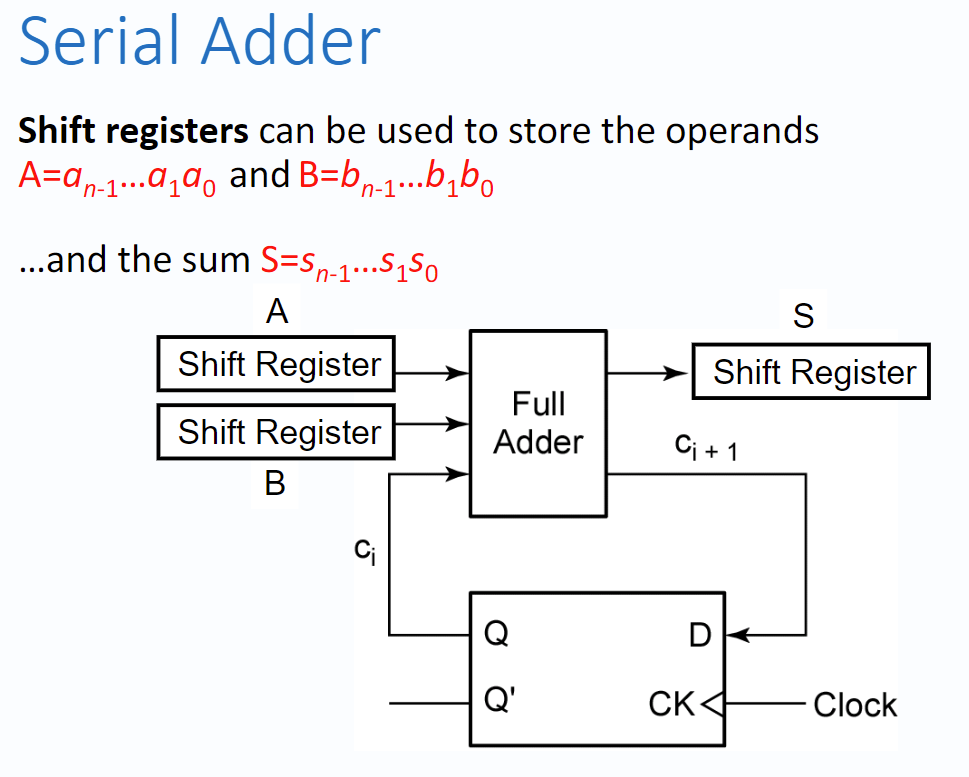

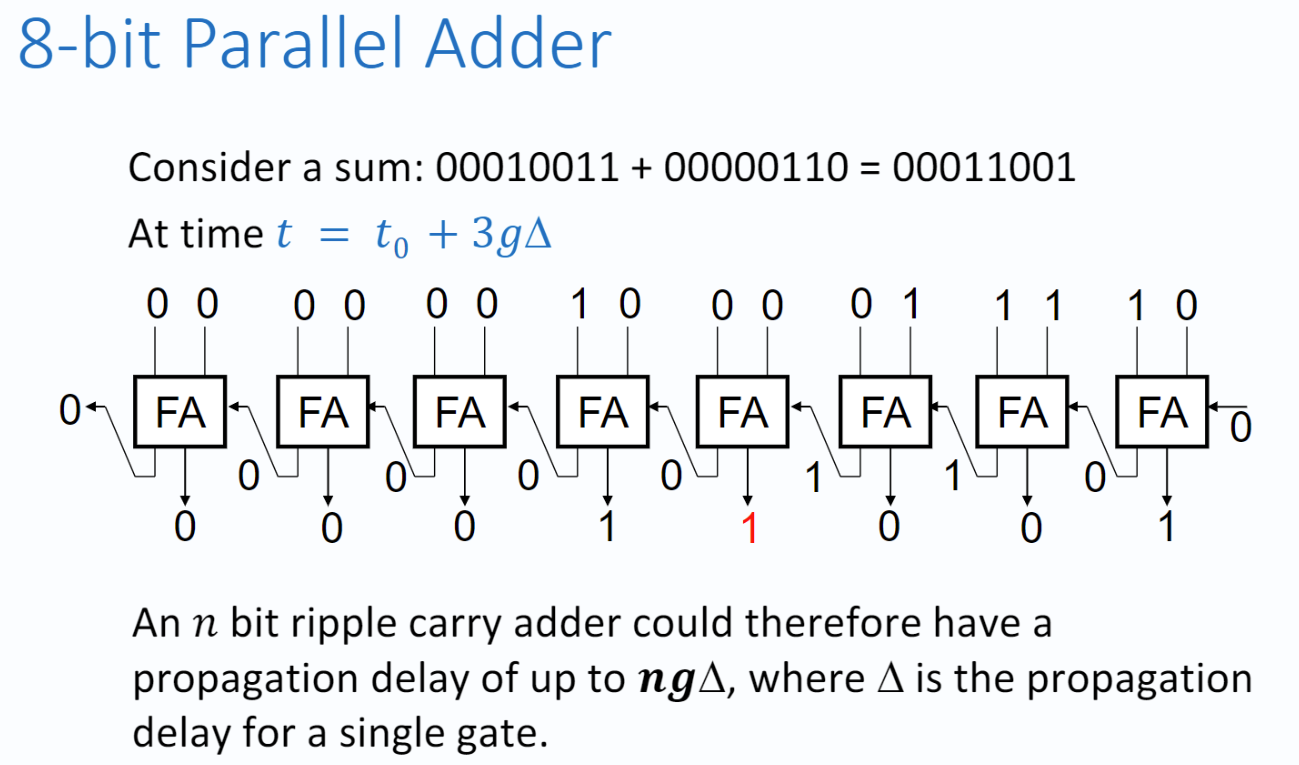

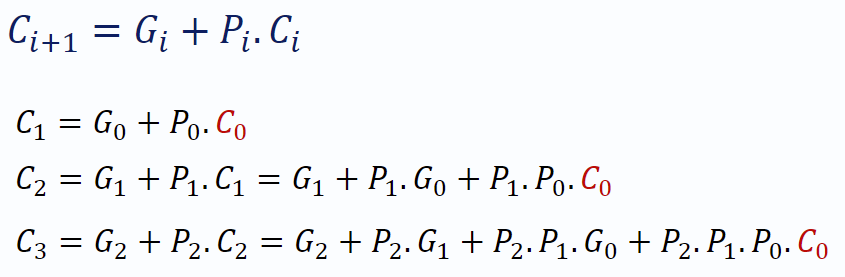

Adder

Parallel ripple carry adder

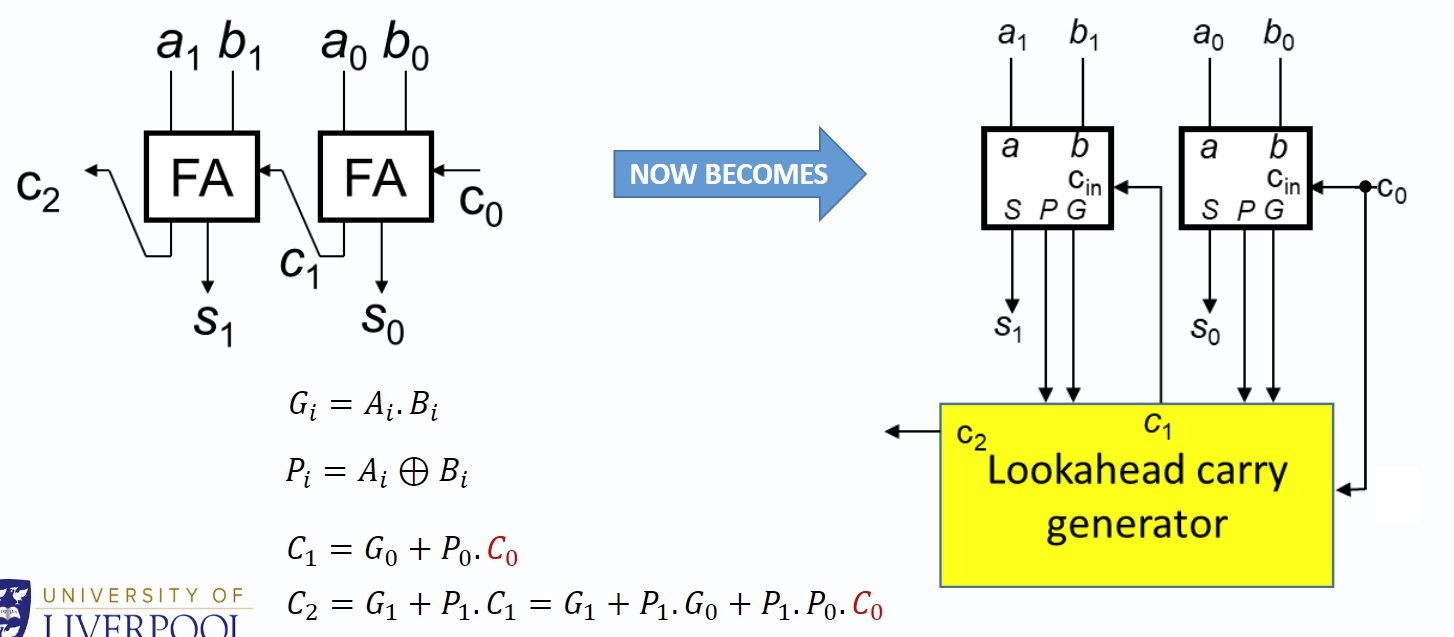

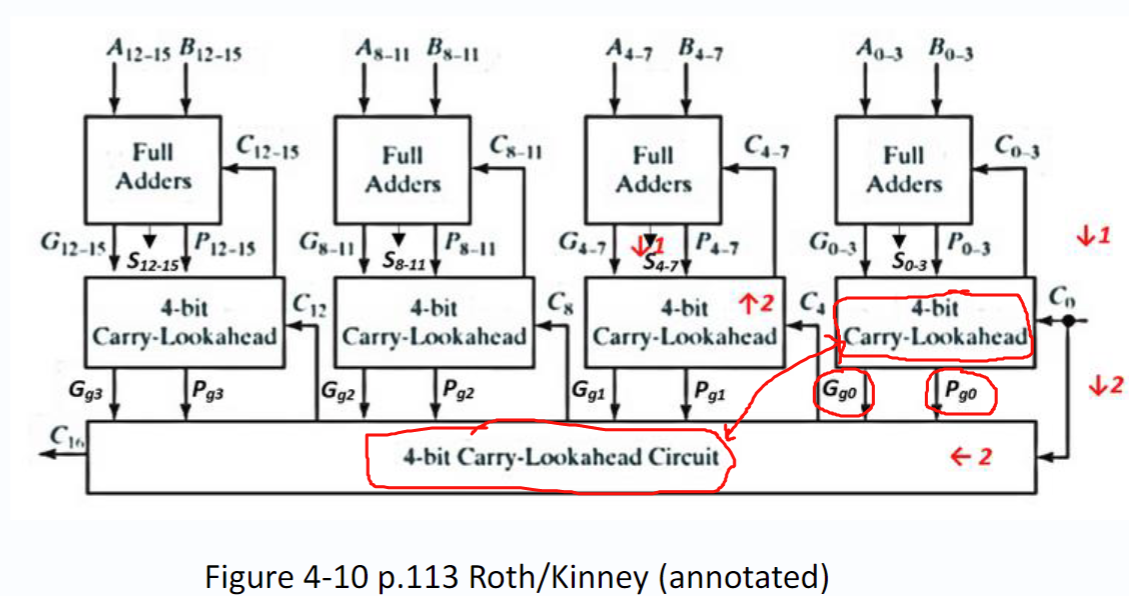

‘carry look ahead’ adder

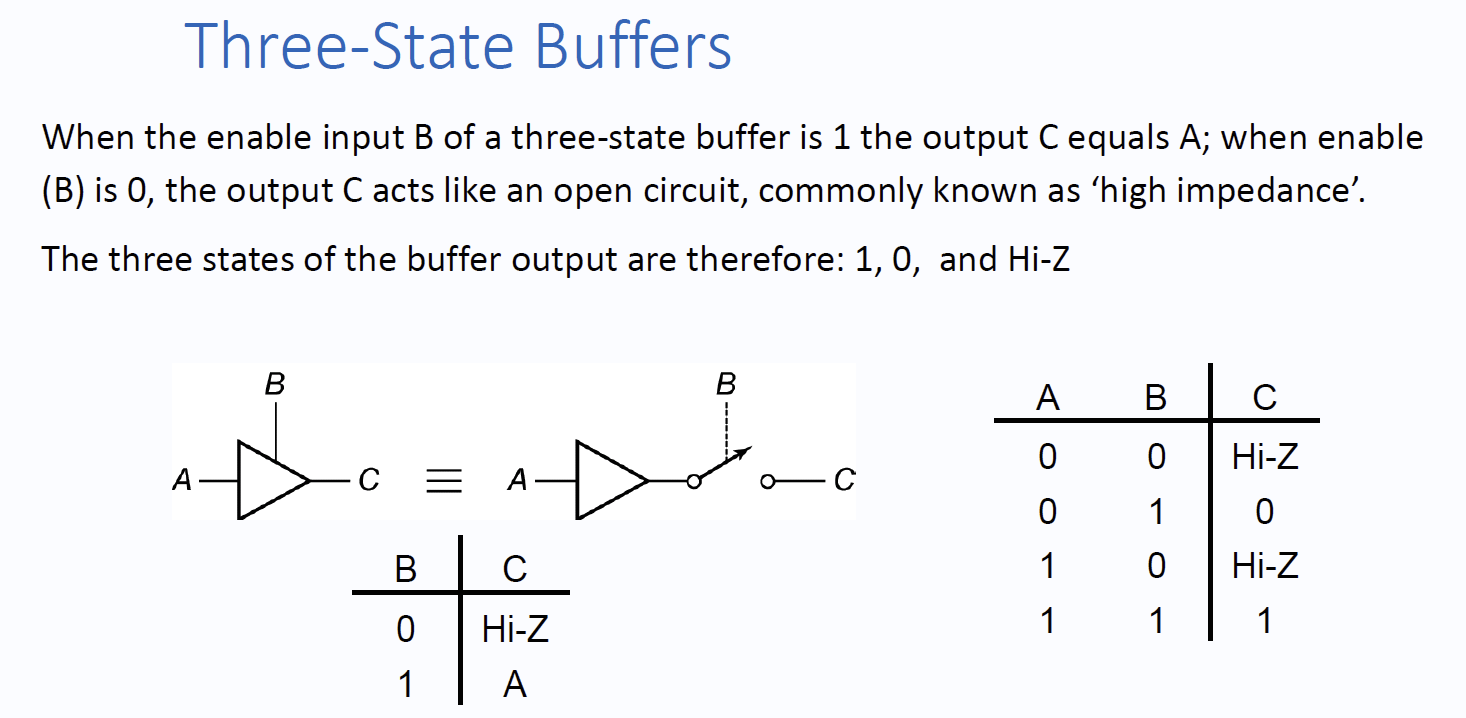

Tristate gates 三态门(three state buffers)

States of Tristate gates:

1,0, high impedance (Hi-Z) 高阻抗 (断路

why?

当多个逻辑电路的输出合并到一条线上,他们的输出会产生冲突:同时短接高低电平,你到底算哪个呢?

此时,Hi-Z提供了解决冲突的方法:多了一种输出——断路。这就意味着,在多个输出里,如果只有一个具有0/1输出而其它都断路的话,那么总输出就必然与0/1输出一致。

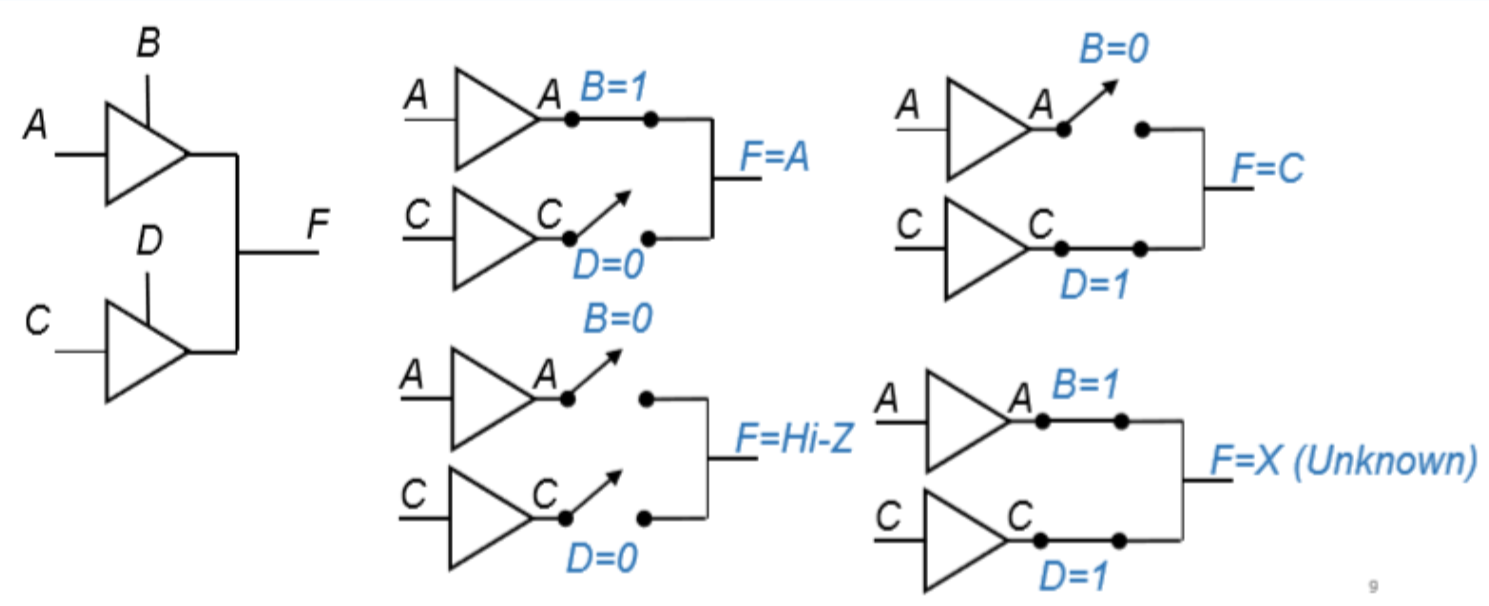

实现:

典中典4种情况:

某种意义上起到了 multiplexer 的作用。

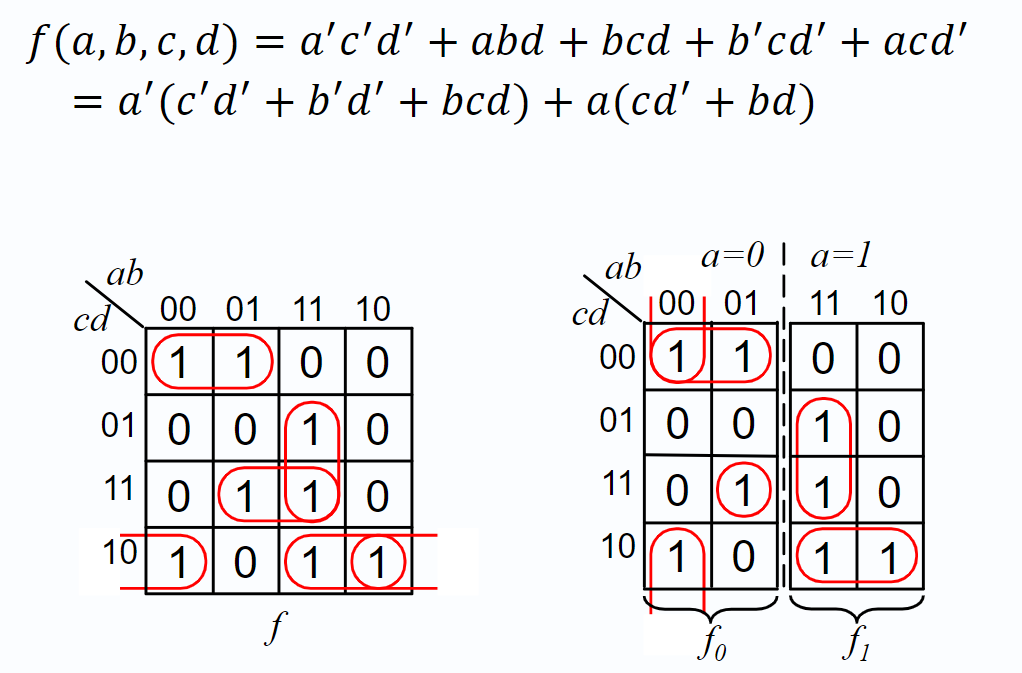

Shannon’s Expansion

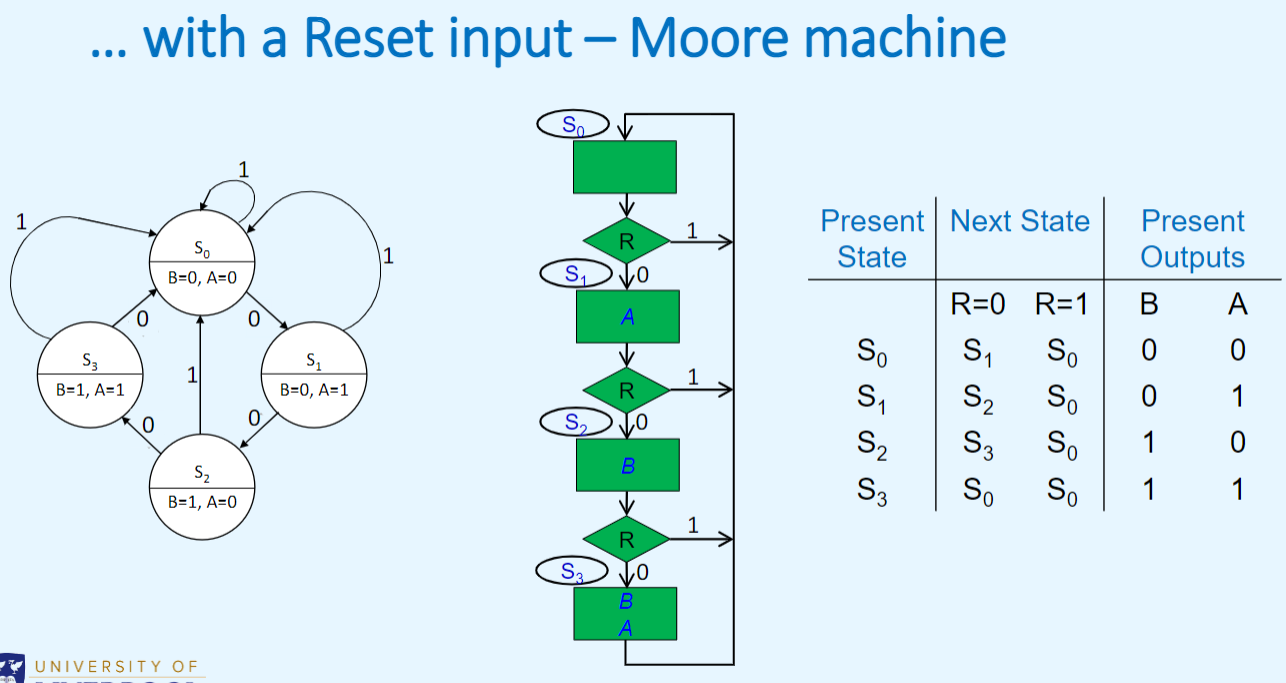

Mealy / Moore machines

In Moore machines, output=f(current state)

In Mealy machines, output=f(current state, input)

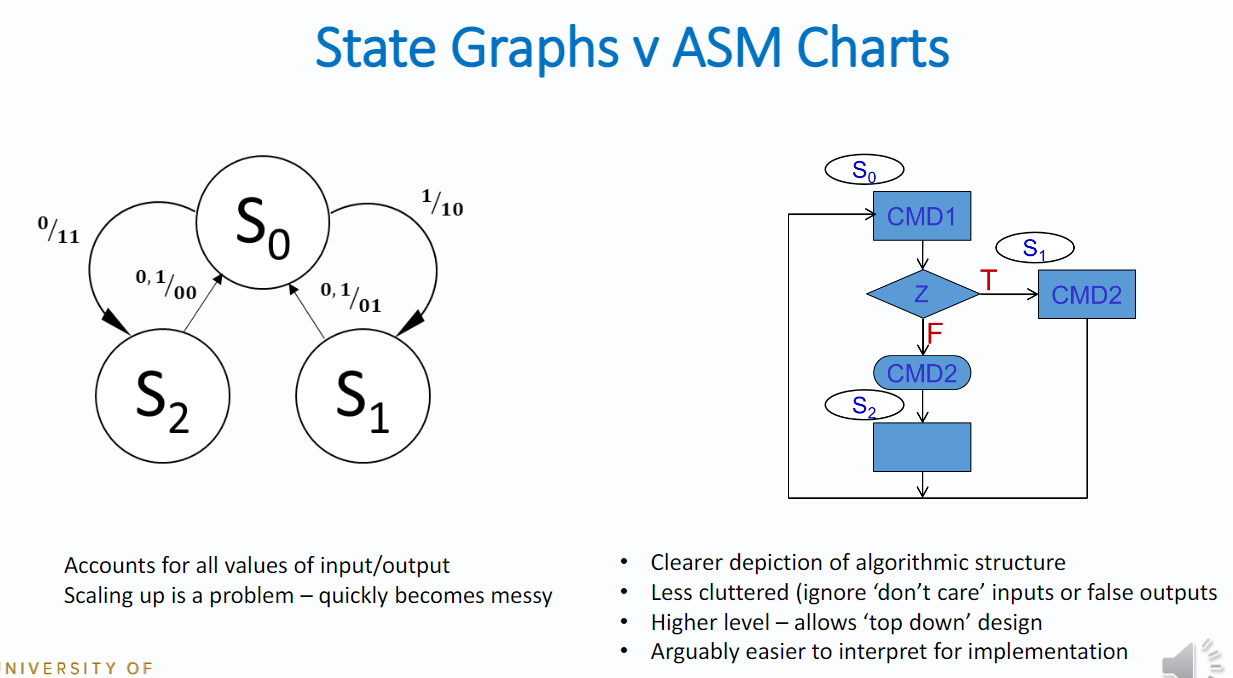

ASM

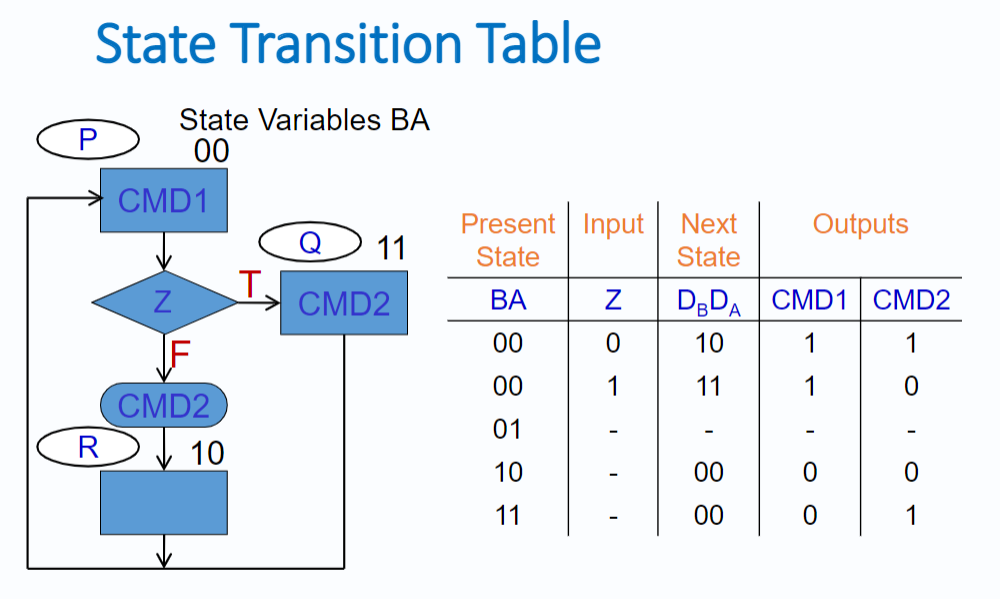

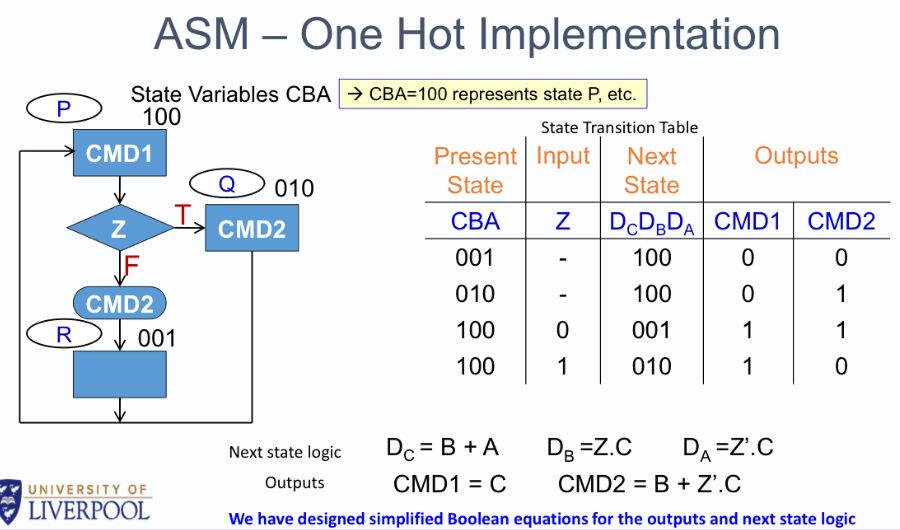

one hot 和 state transition 是同一种表格

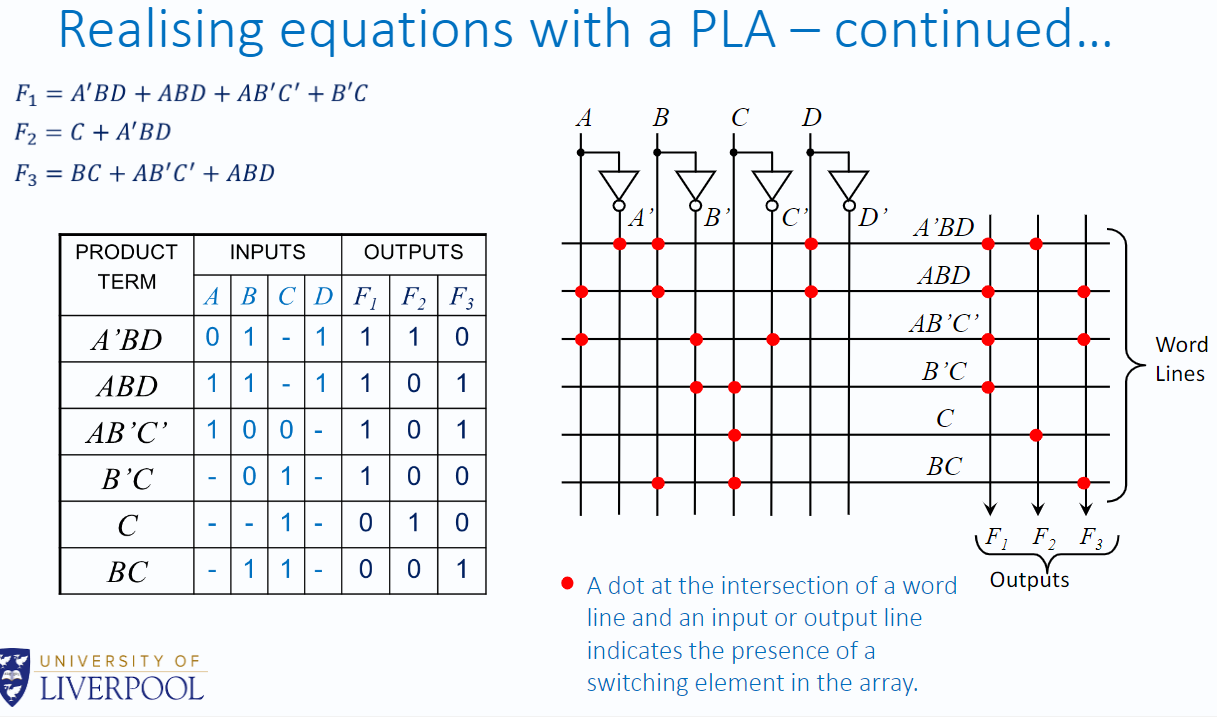

PLA table: 其实差不多,但是用于设计PLA:

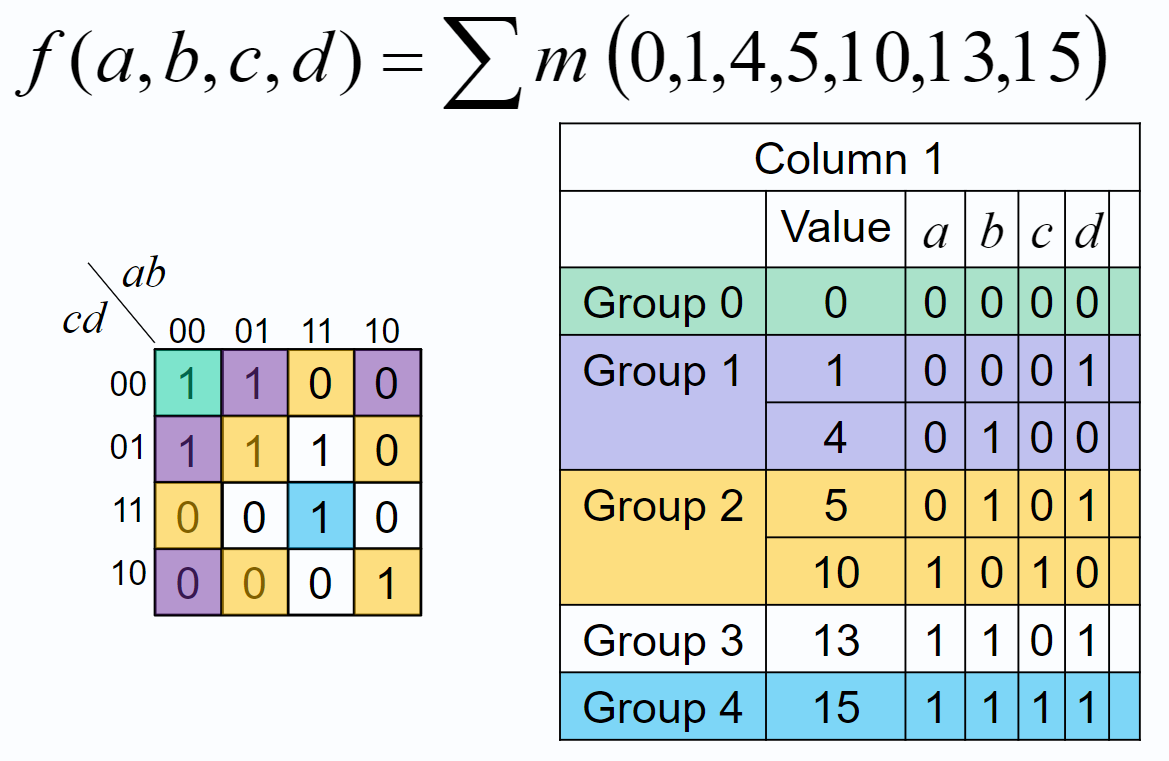

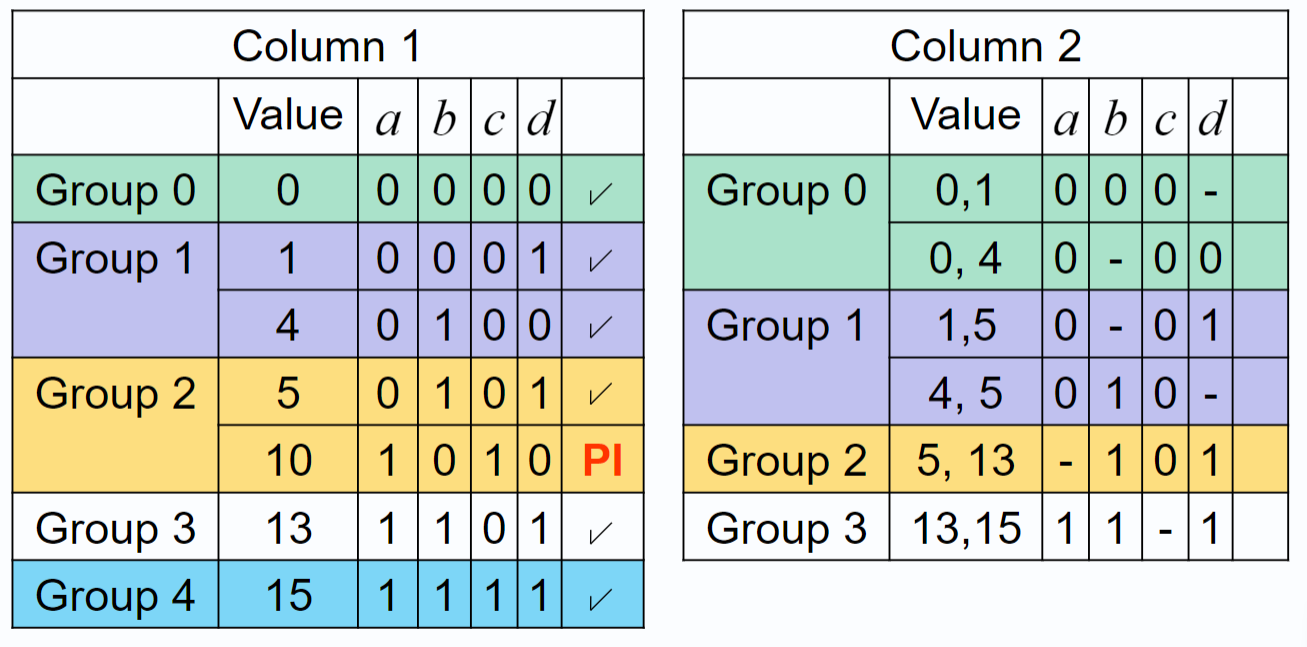

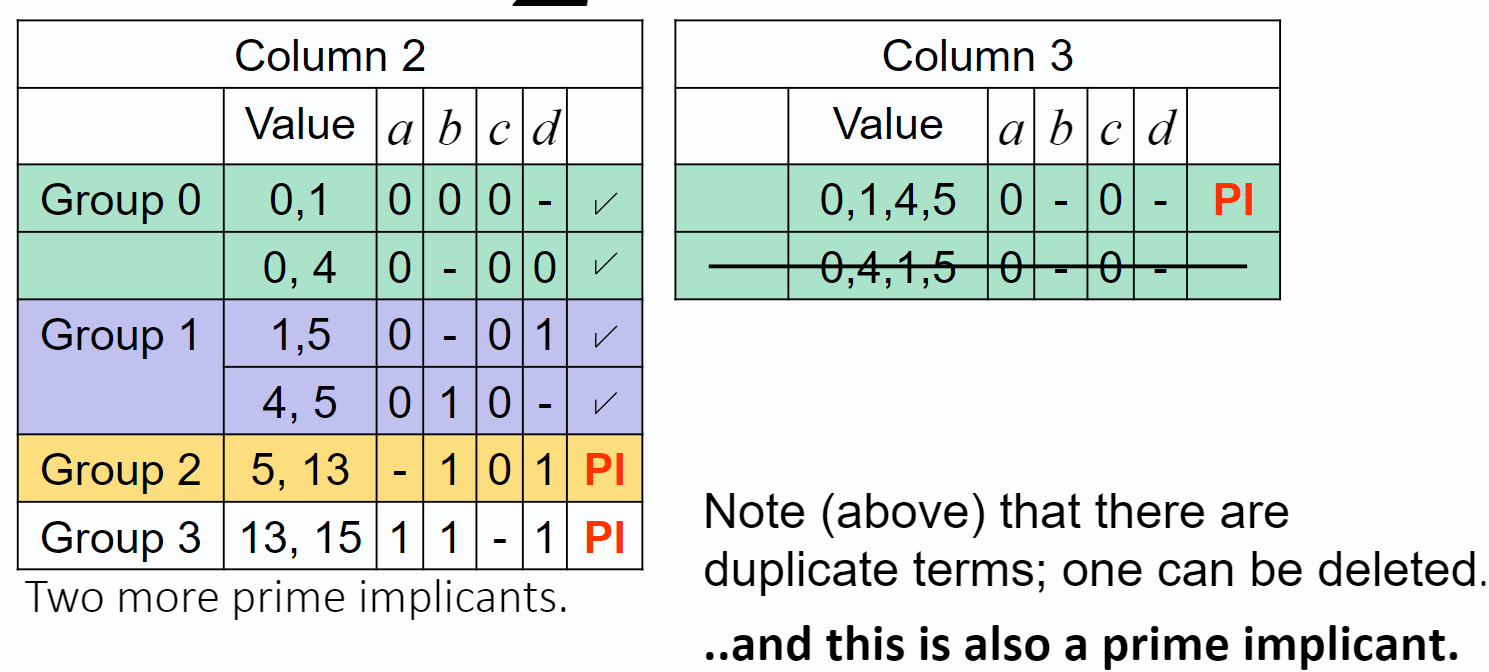

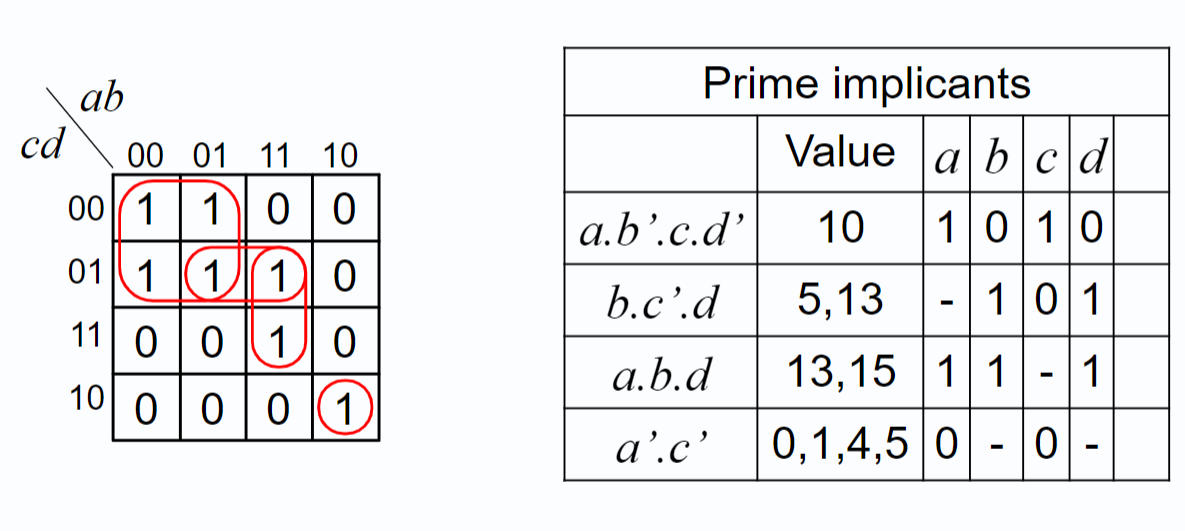

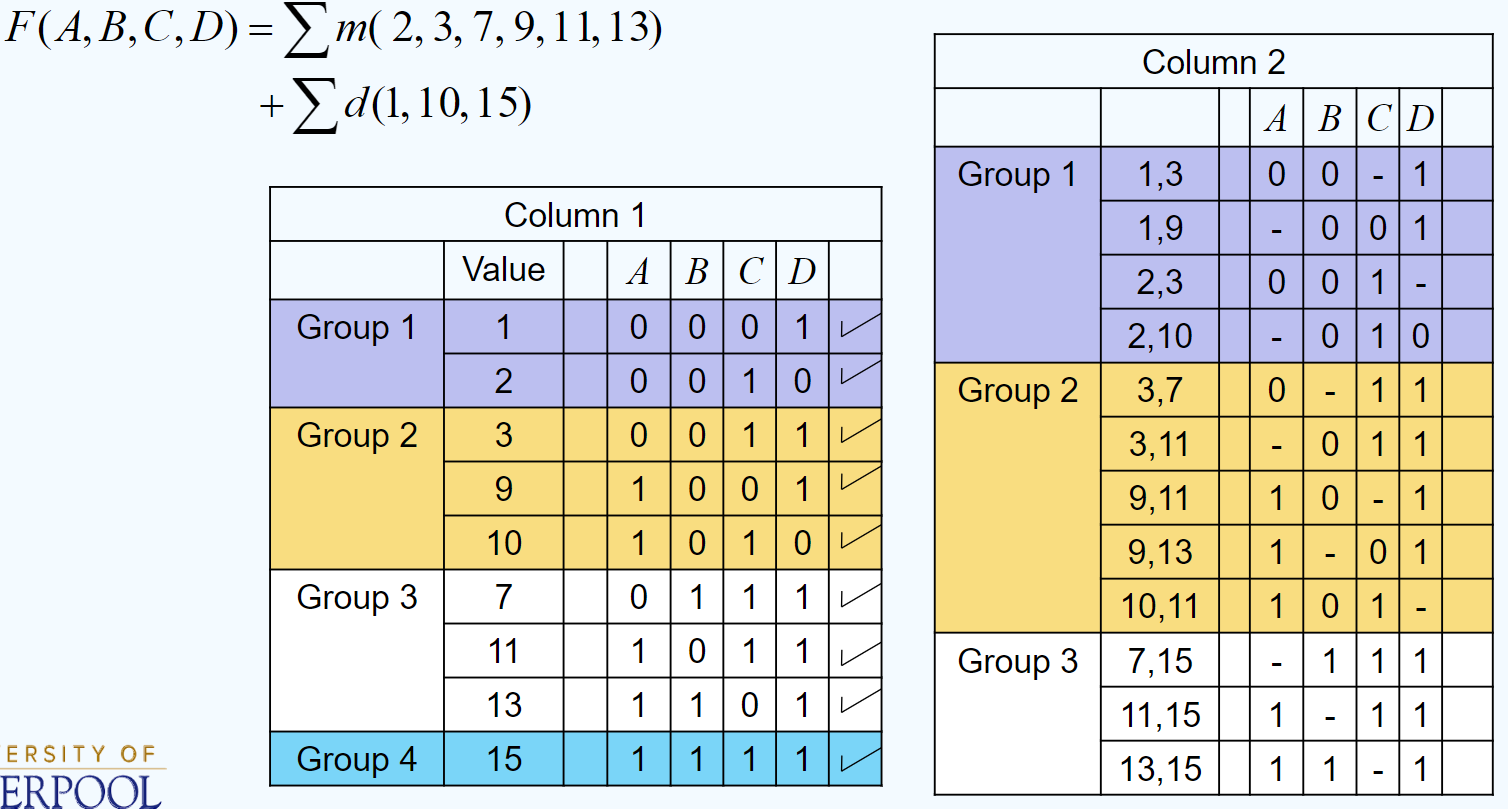

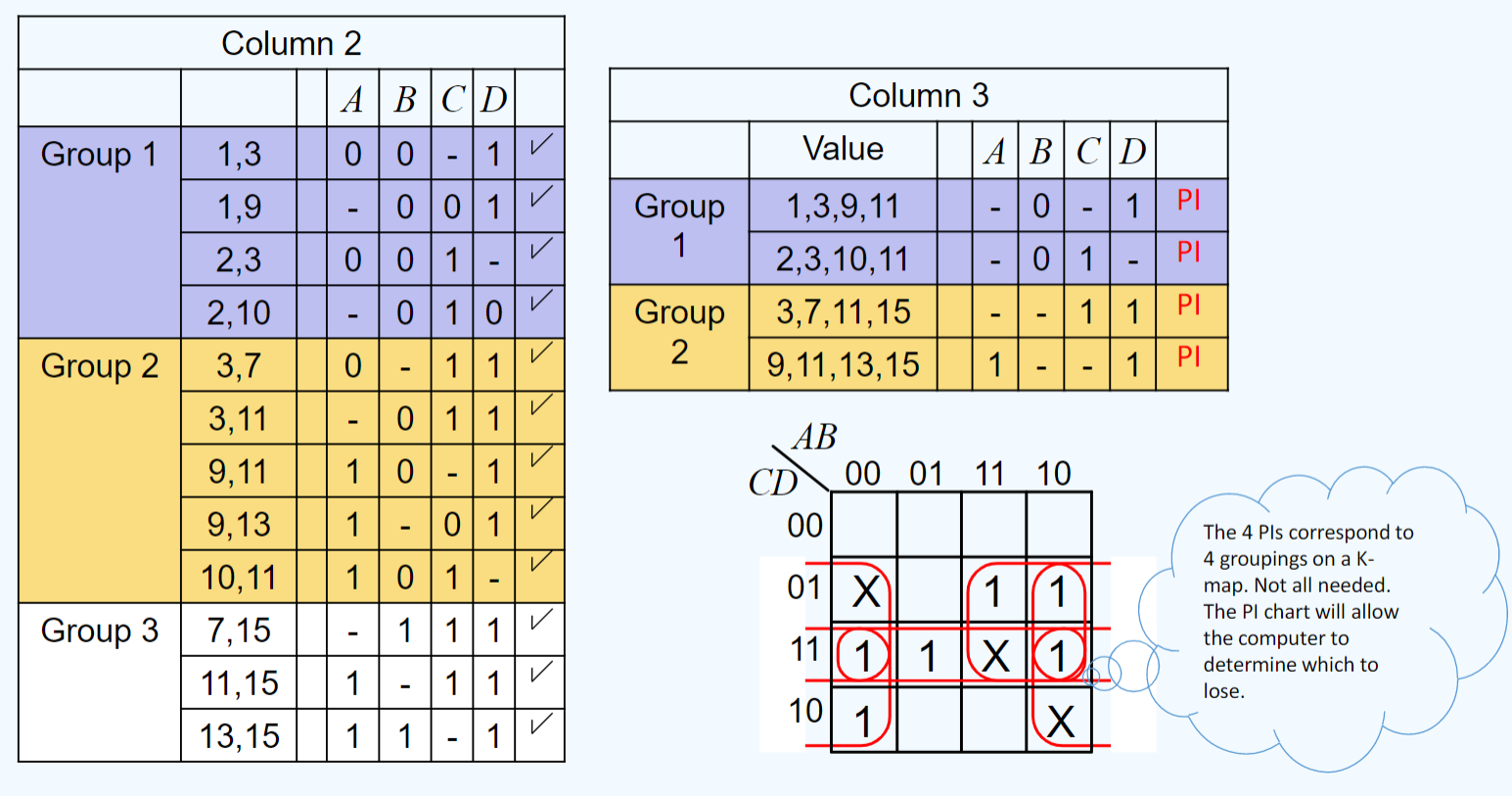

Quine-McCluskey

无 d

有 d,Incompletely Specified Functions

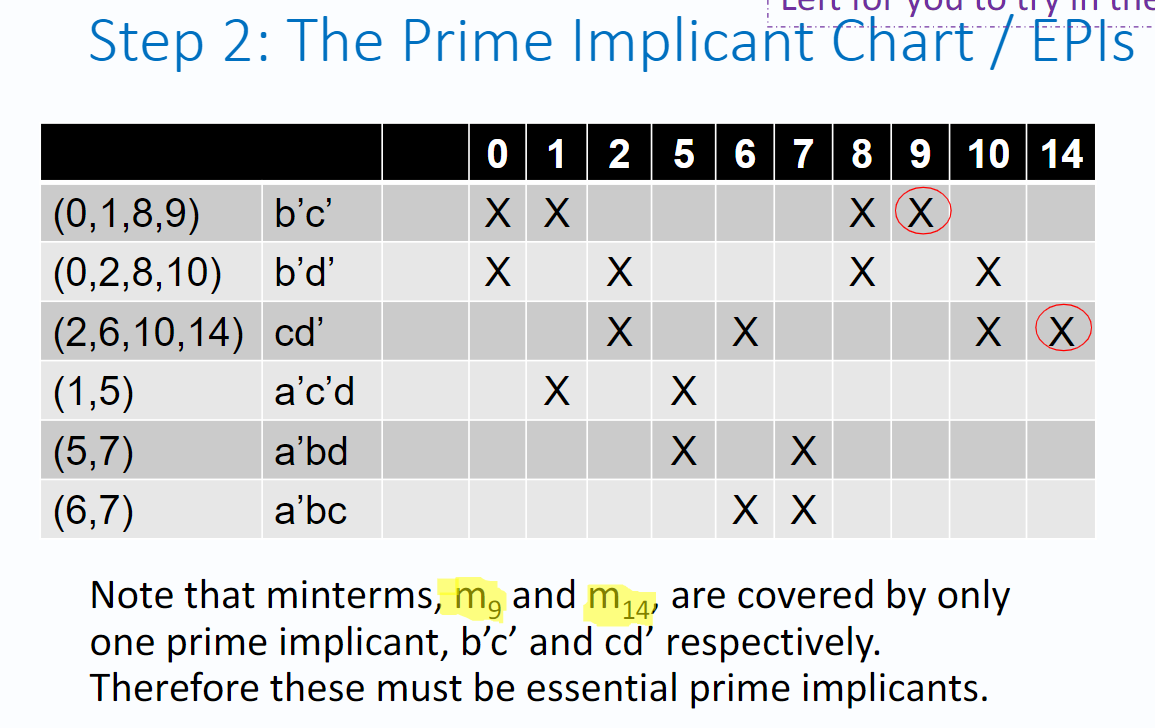

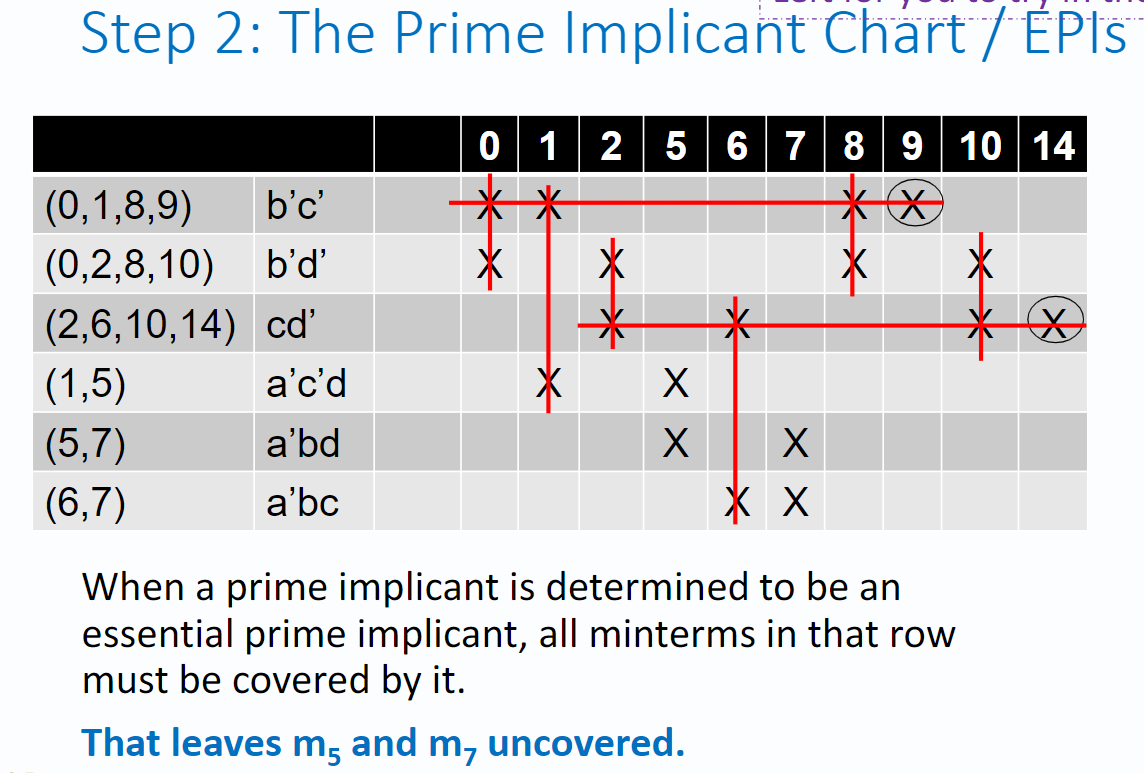

找到所有的PI 后,找EPI

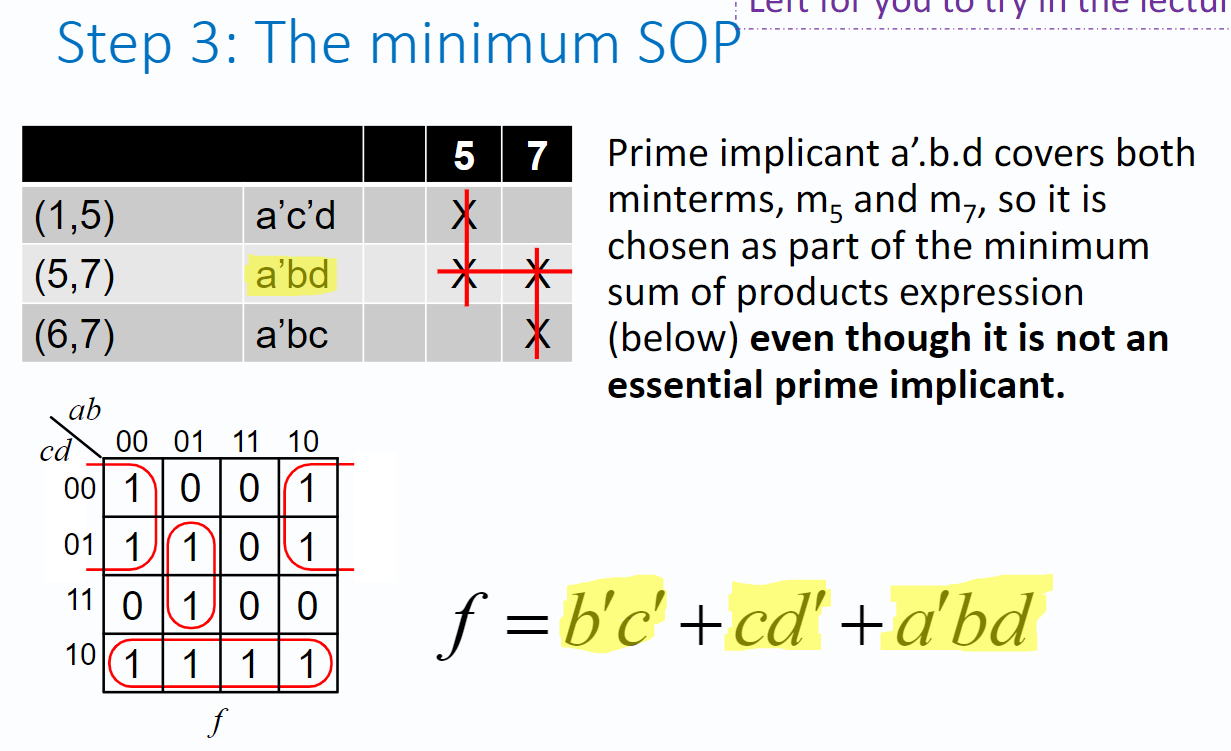

然后找SOP

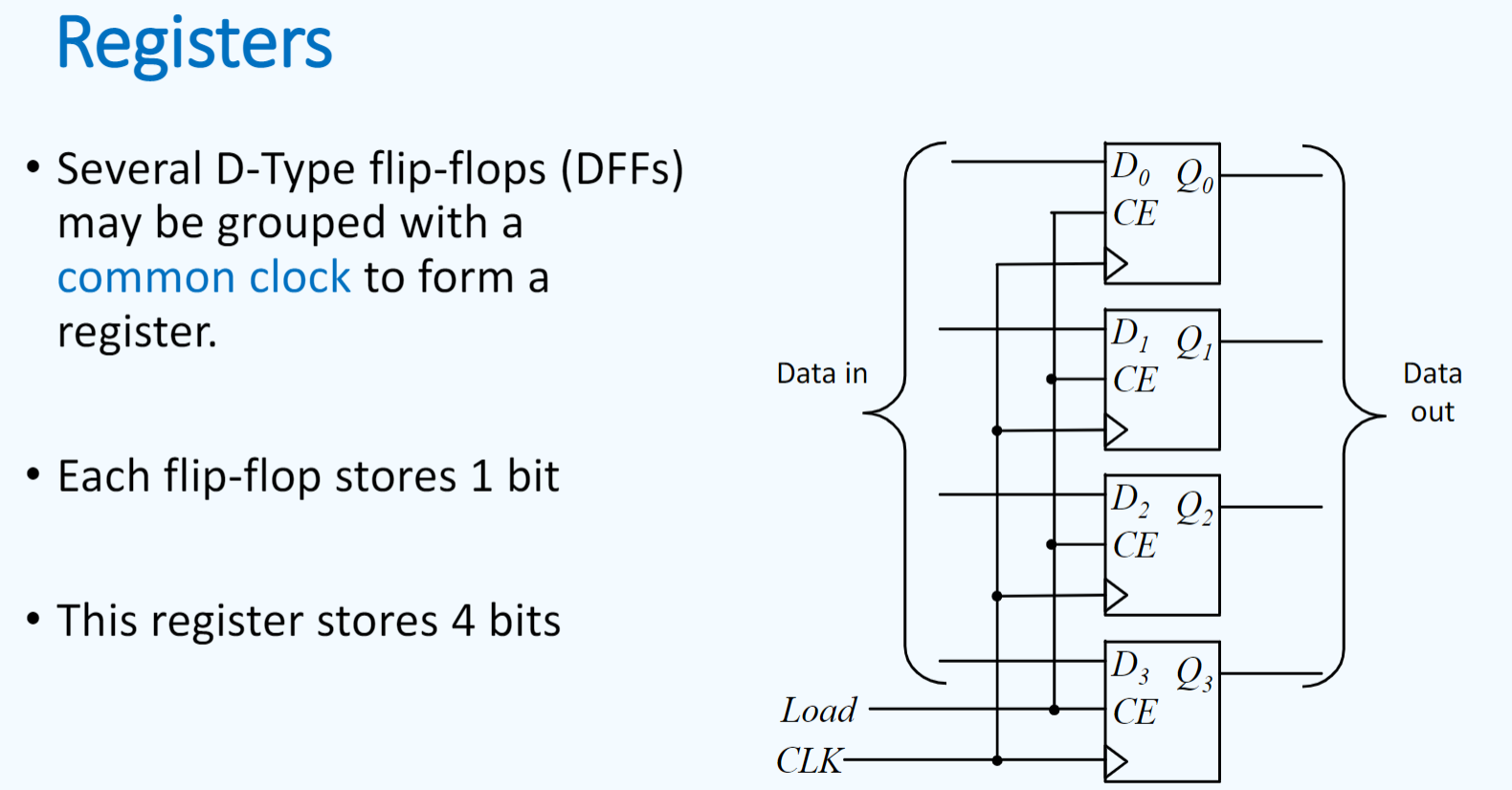

Registers

use D Flip-Flops with Clock Enable

When Load is 1 the clock is enabled (CE) and the data applied to the D inputs will be loaded into the flip-flops.

When Load is 0 the register holds its data (memory).

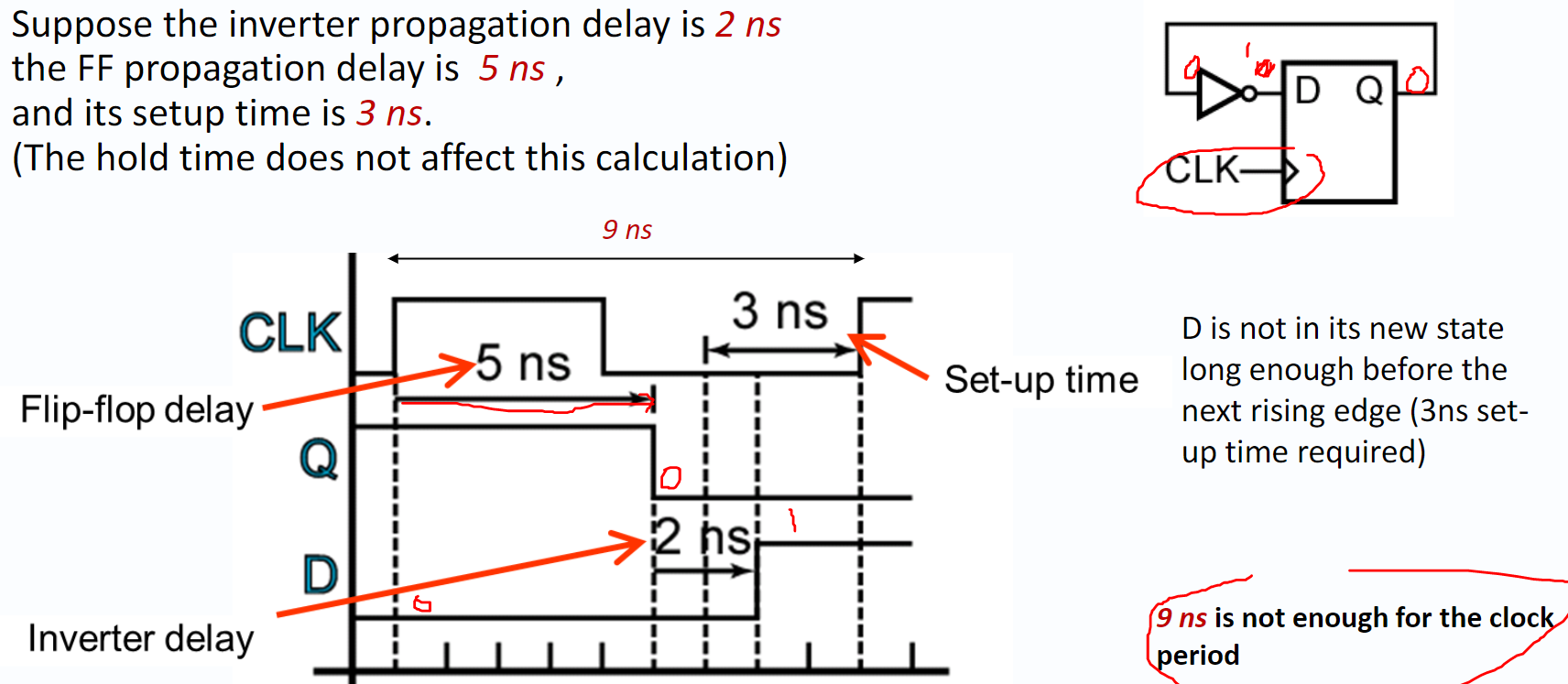

D Flip-Flop

Minimum Clock Period = flip-flop propagation delay + setup time + propagation delay of other components in circuit

------------------------Microprocessor Systems------------------------

Shift-register

LSLS - logical shift left: abcdefghijkl => defghijkl000

LSRS - logical shift right: abcdefghijkl => 000abcdefghi

ASRS - Arithmetic shift right: abcdefghijkl => aaaabcdefghi *a是符号位

PORS - Rotate right: abcdefghijkl => jklabcdefghi *j当carry

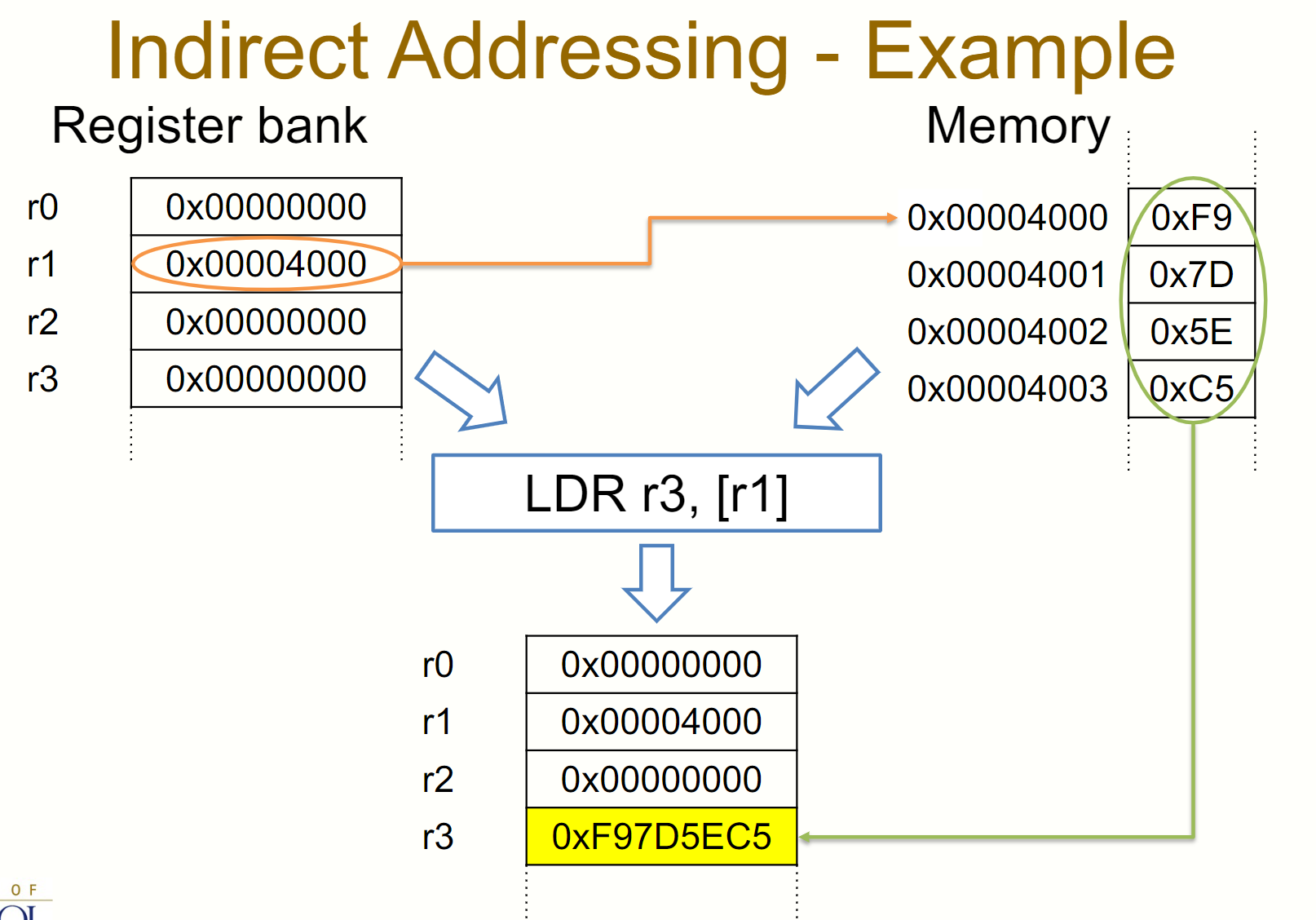

addressing

after LDR rd, [rn]

| registers | value in registers | memory | value in memory |

|---|---|---|---|

| rd(initial) | 0xABCDEFGH | 0x00008000 | 12 |

| rn | 0x00008000 | 0x00008001 | 34 |

| rd(Big endian) | 0x12345678 | 0x00008002 | 56 |

| rd(Little endian) | 0x78563412 | 0x00008003 | 78 |

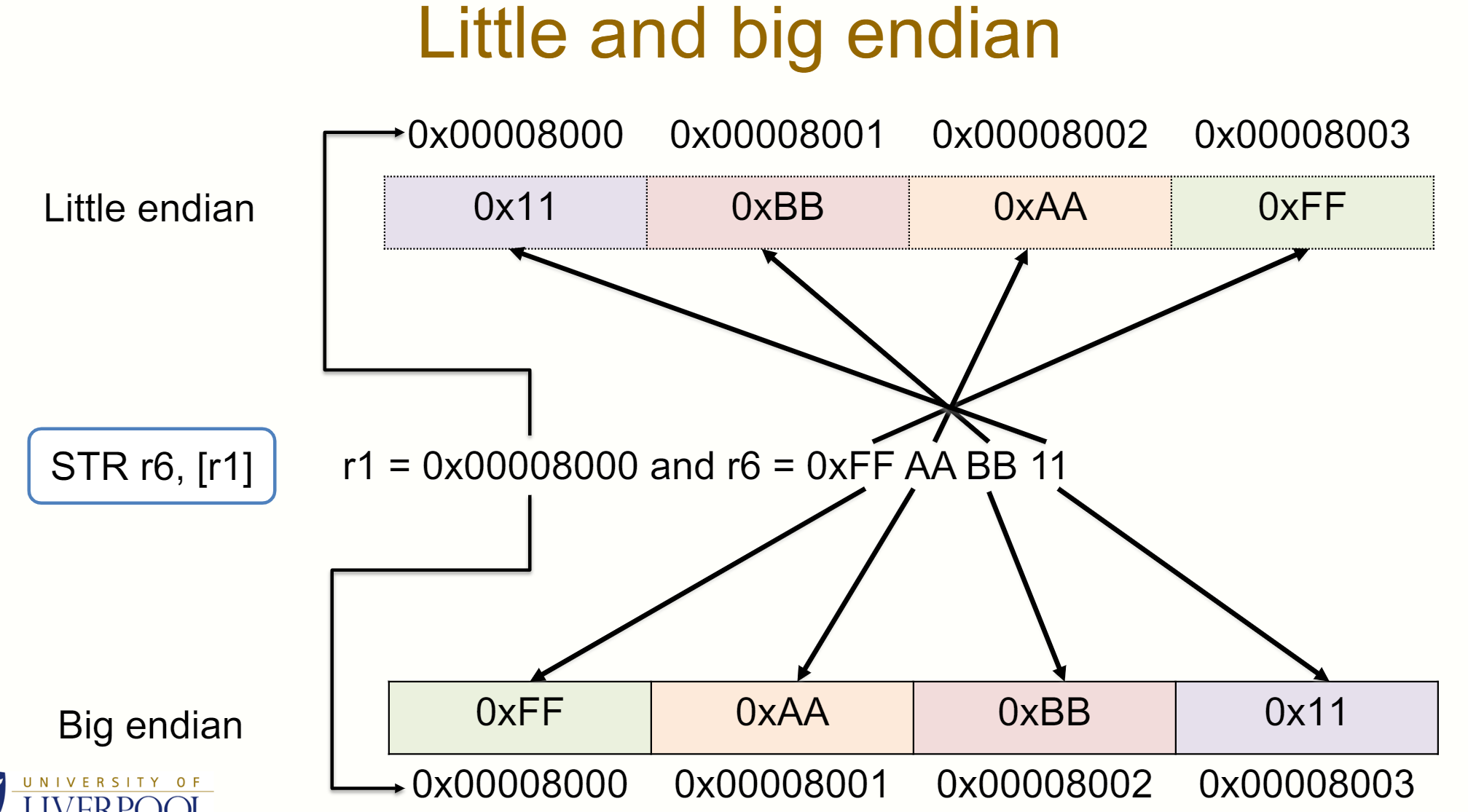

after STR rd, [rn]

| registers | value in registers | memory | Big endian | Little endian |

|---|---|---|---|---|

| rd | 0xABCDEFGH | 0x00008000 | AB | GH |

| rn | 0x00008000 | 0x00008001 | CD | EF |

| 0x00008002 | EF | CD | ||

| 0x00008003 | GH | AB |

REV ry, rx // Little endian <-> Big endian, y <-- x

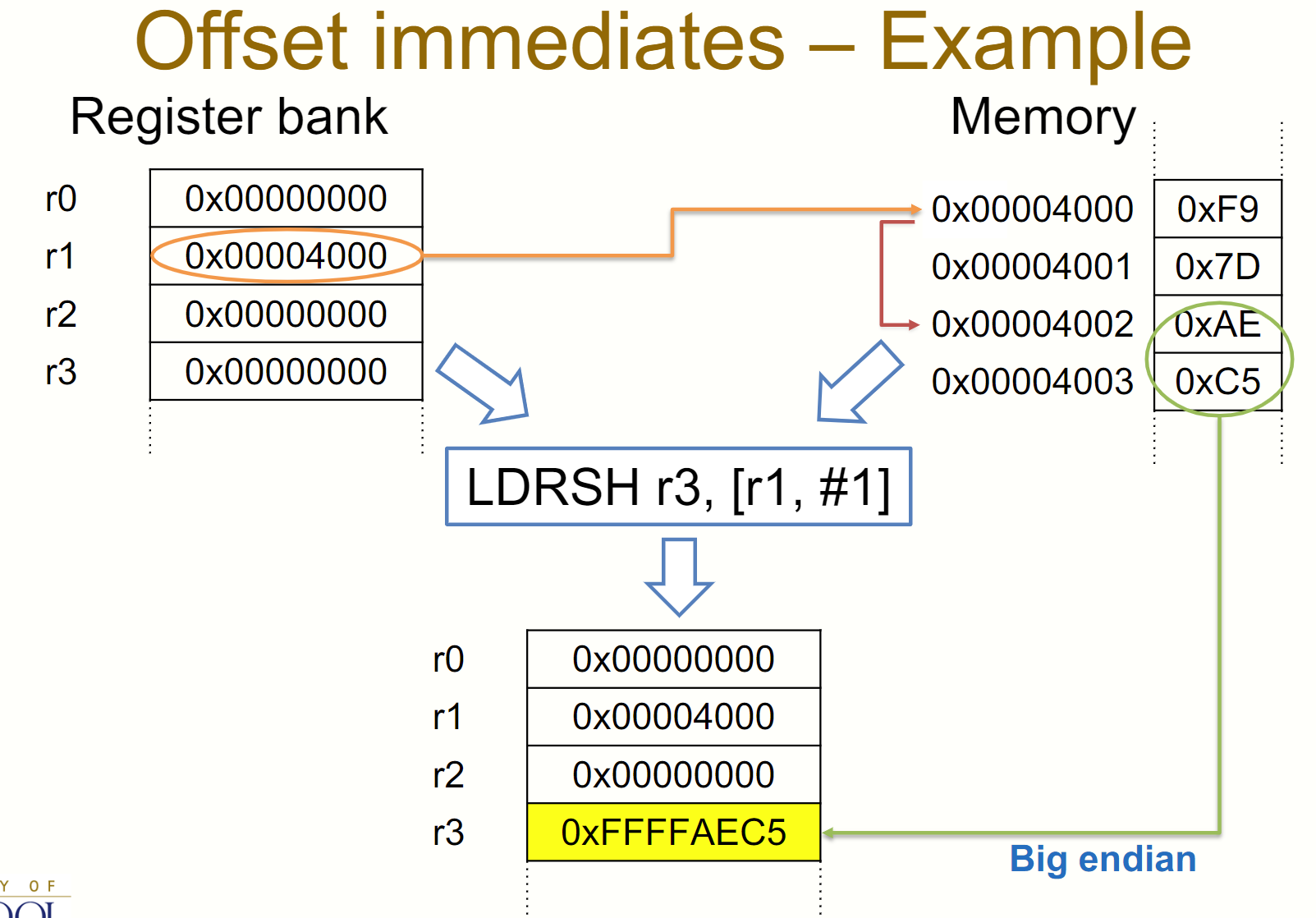

LDR: load full word (32 bits)

LDRH: load half word (16 bits)(0000XXXX)

LDRB: load byte (8 bits)(000000XX)

LDRSH/LDRSB: load with the sign (S...SX...X)

STRH: Store half word

#的偏移也会随着存入数据的大小改变:

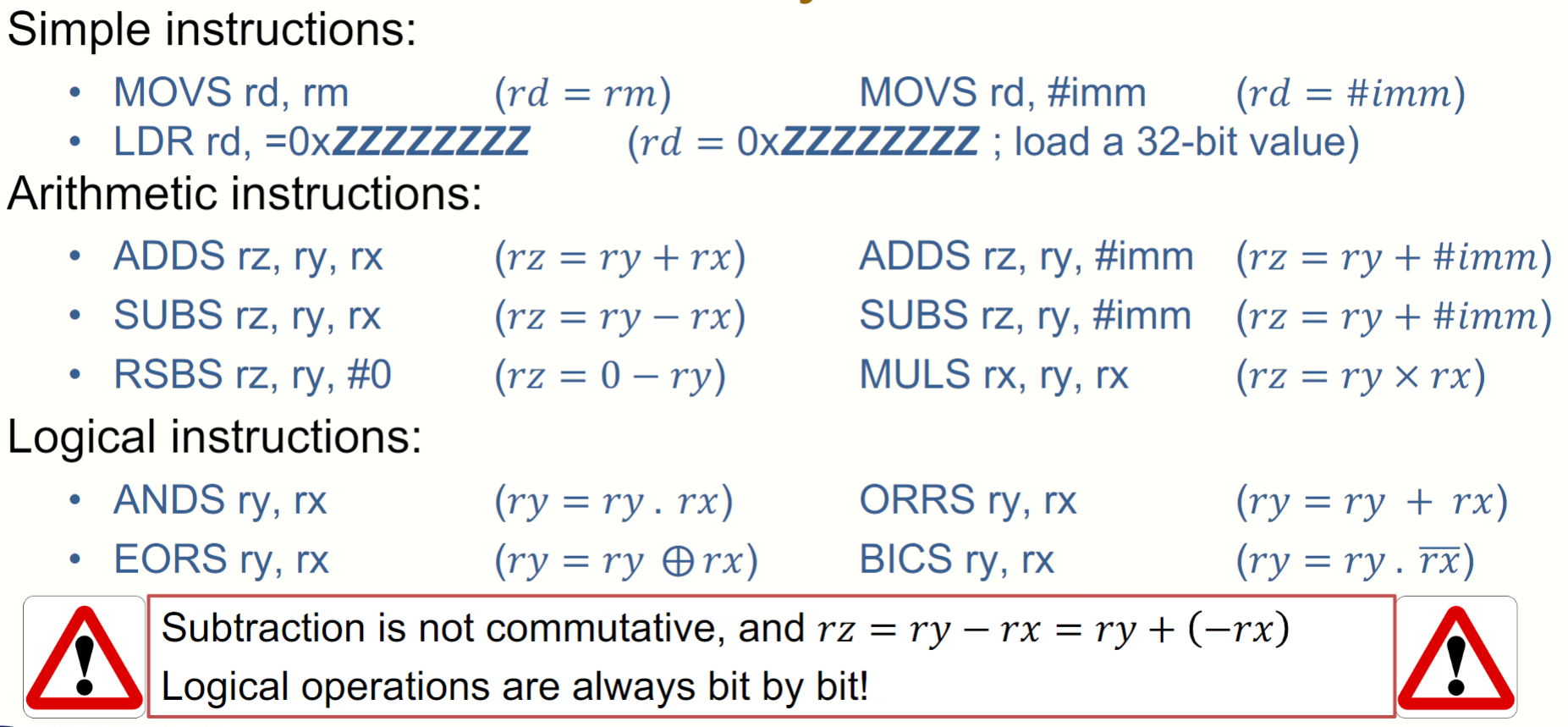

instructions:

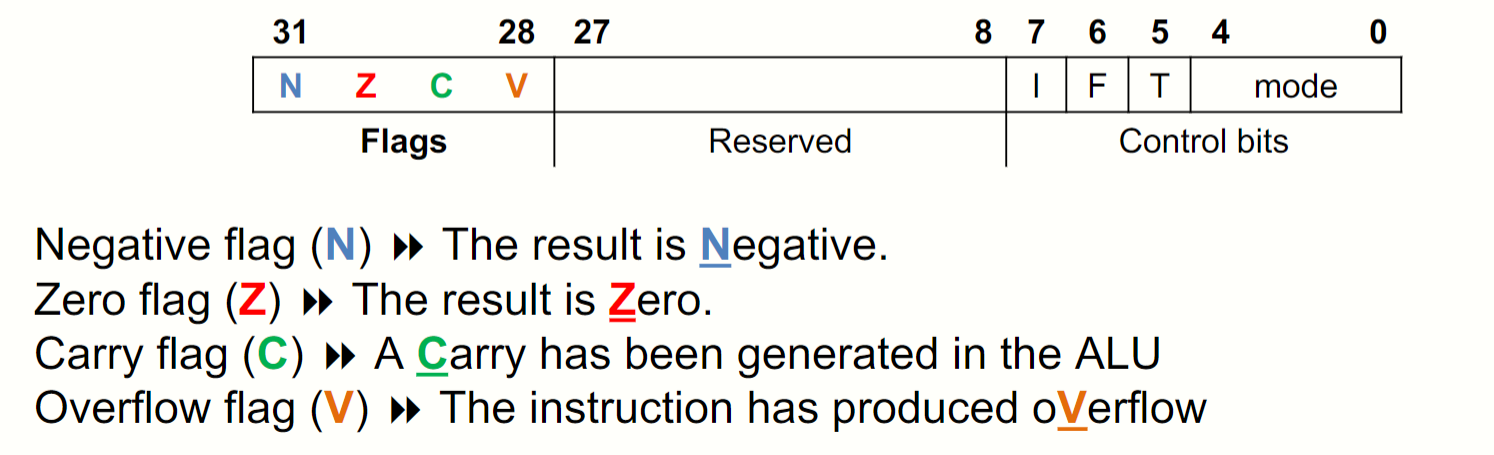

Flags

注意, 当运算的结果产生进位或者减法运算没有借位的话C=1,其他情况C=0

Carry vs Overflow

carry: 无符号溢出

Overflow:有符号溢出

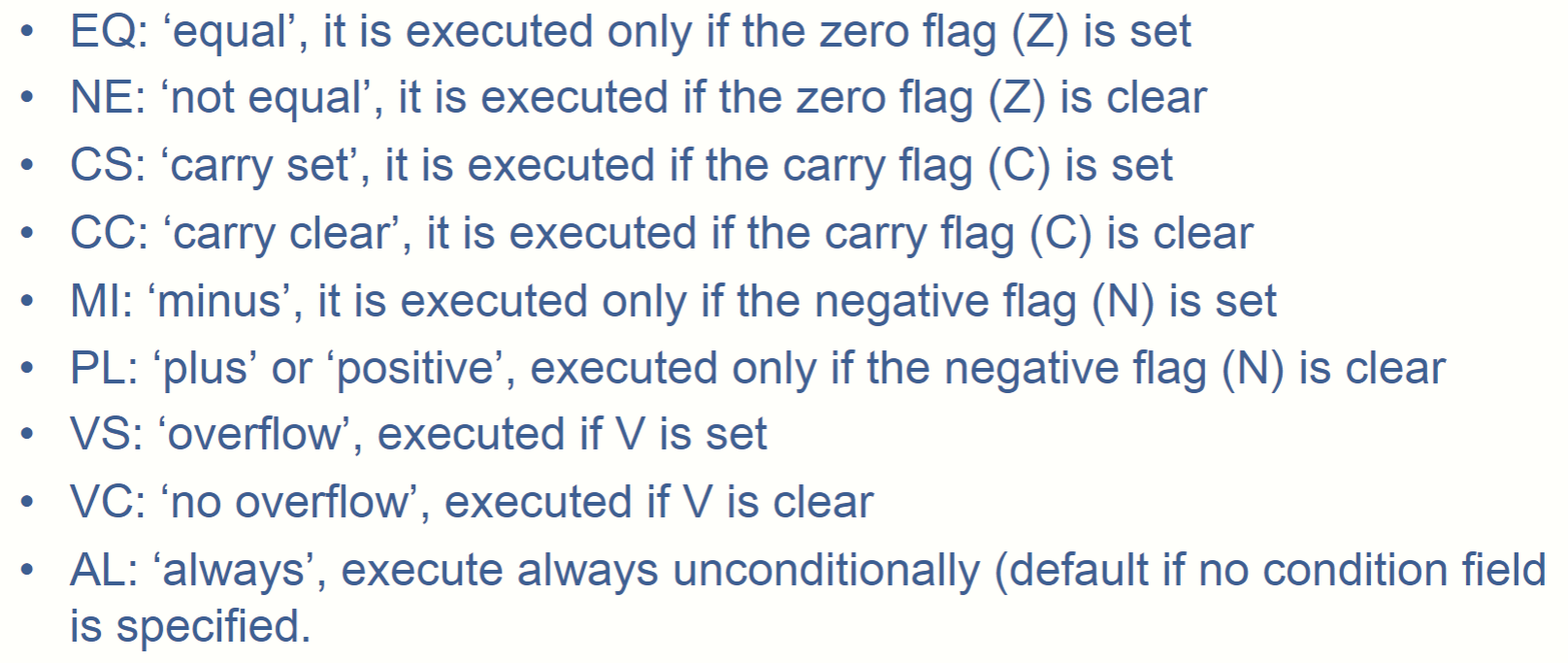

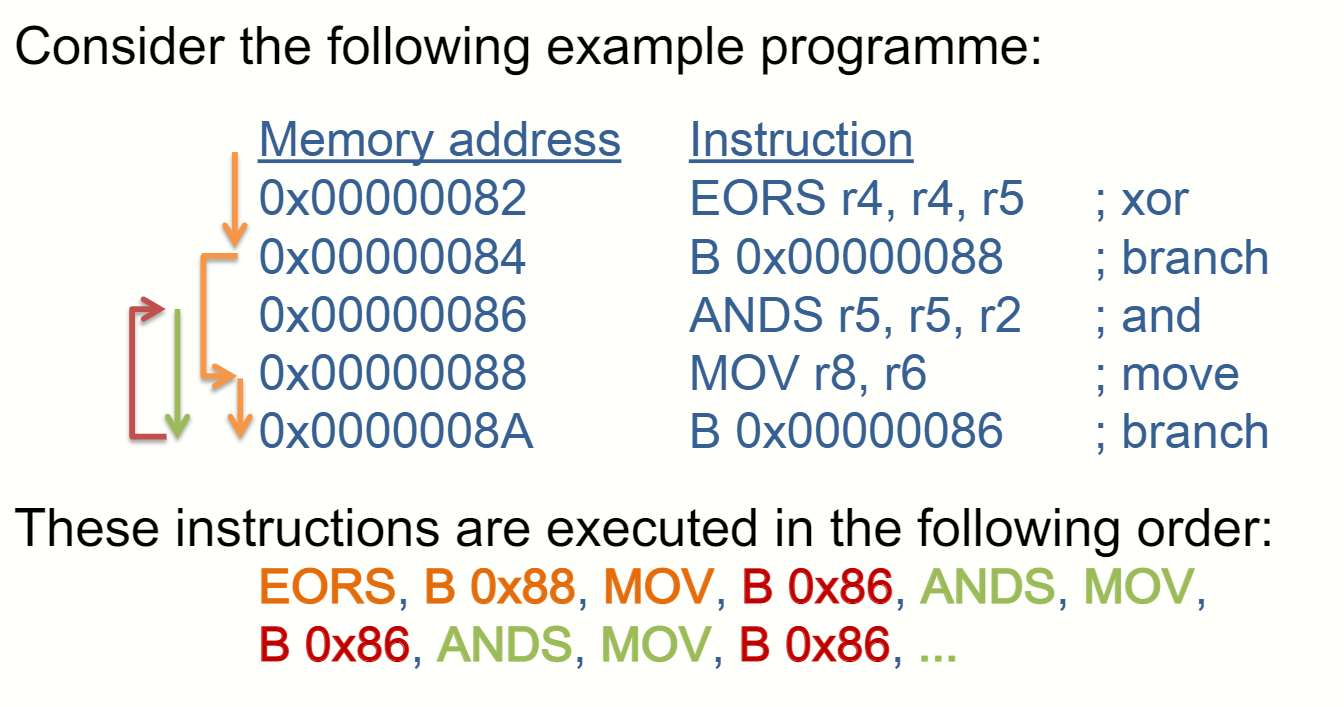

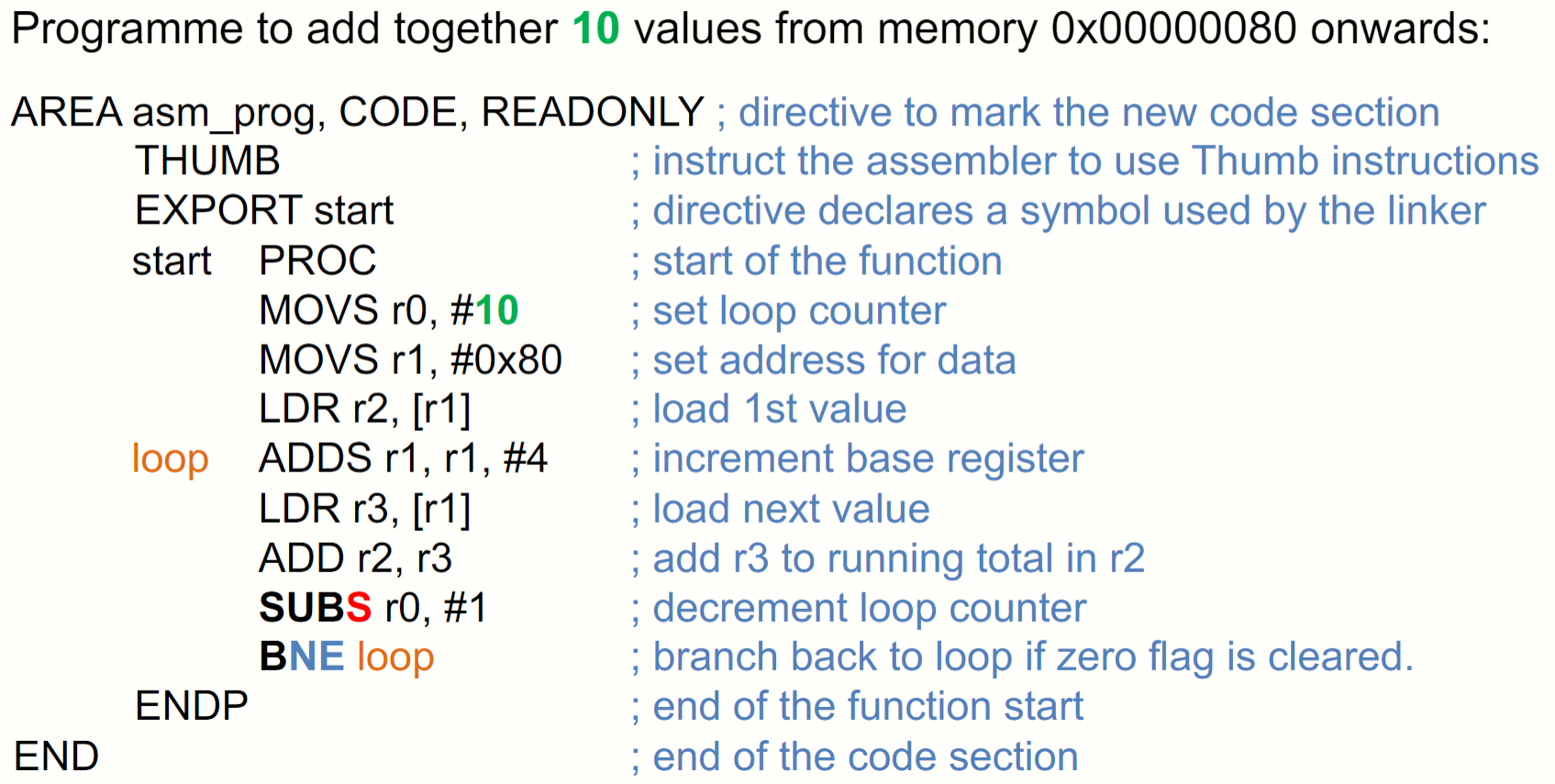

Branch

B

B<cond>

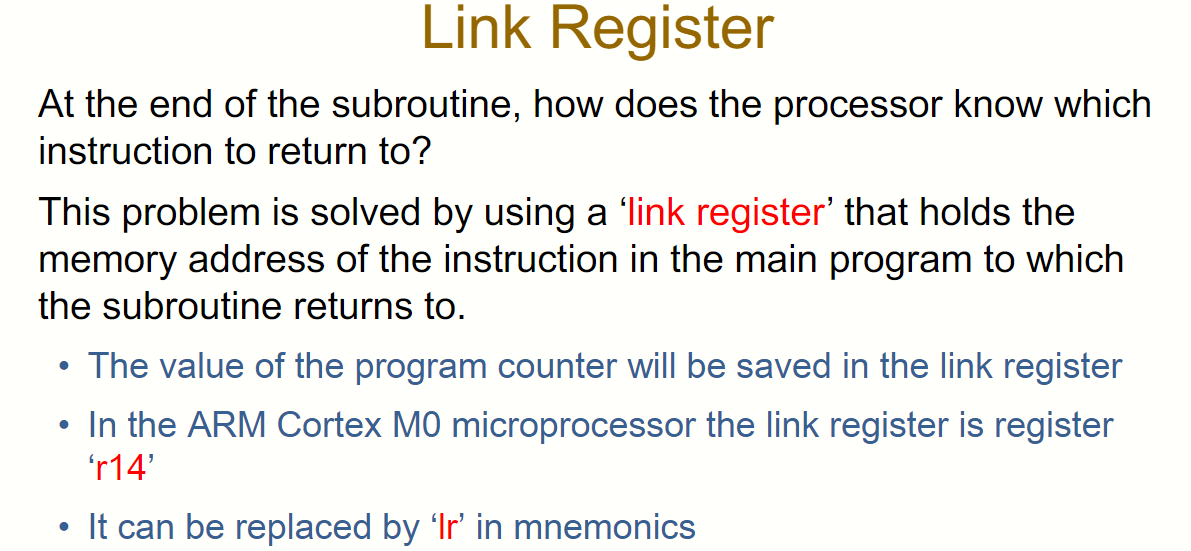

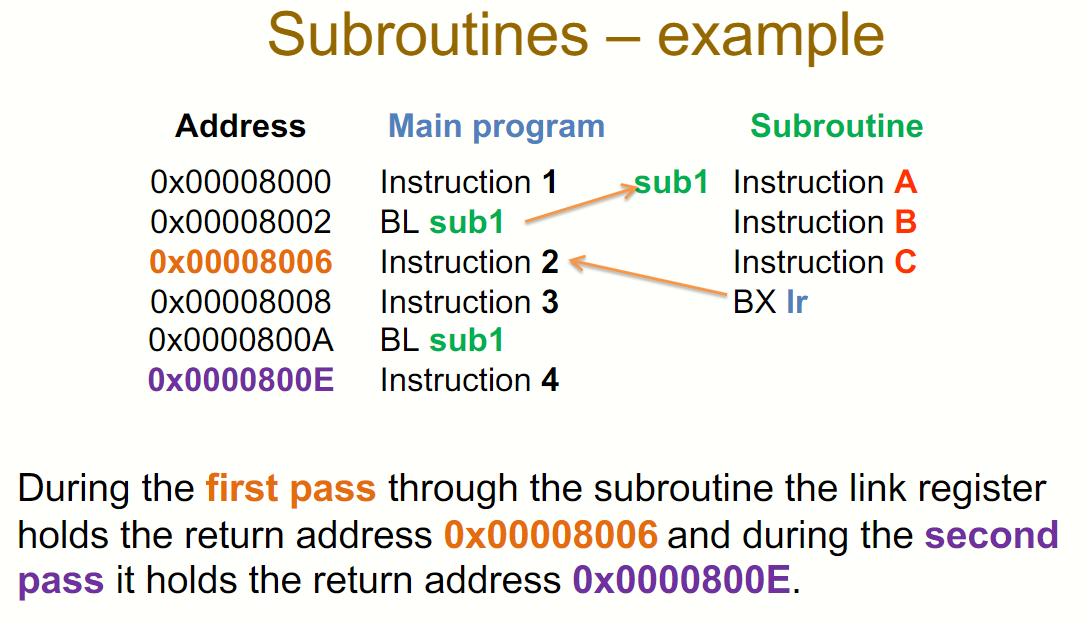

PC vs LR vs SR

PC: program counter, R15

存放下一次访存的地址。

SR: stack pointer

栈顶

LR: link register, R14

函数的返回地址

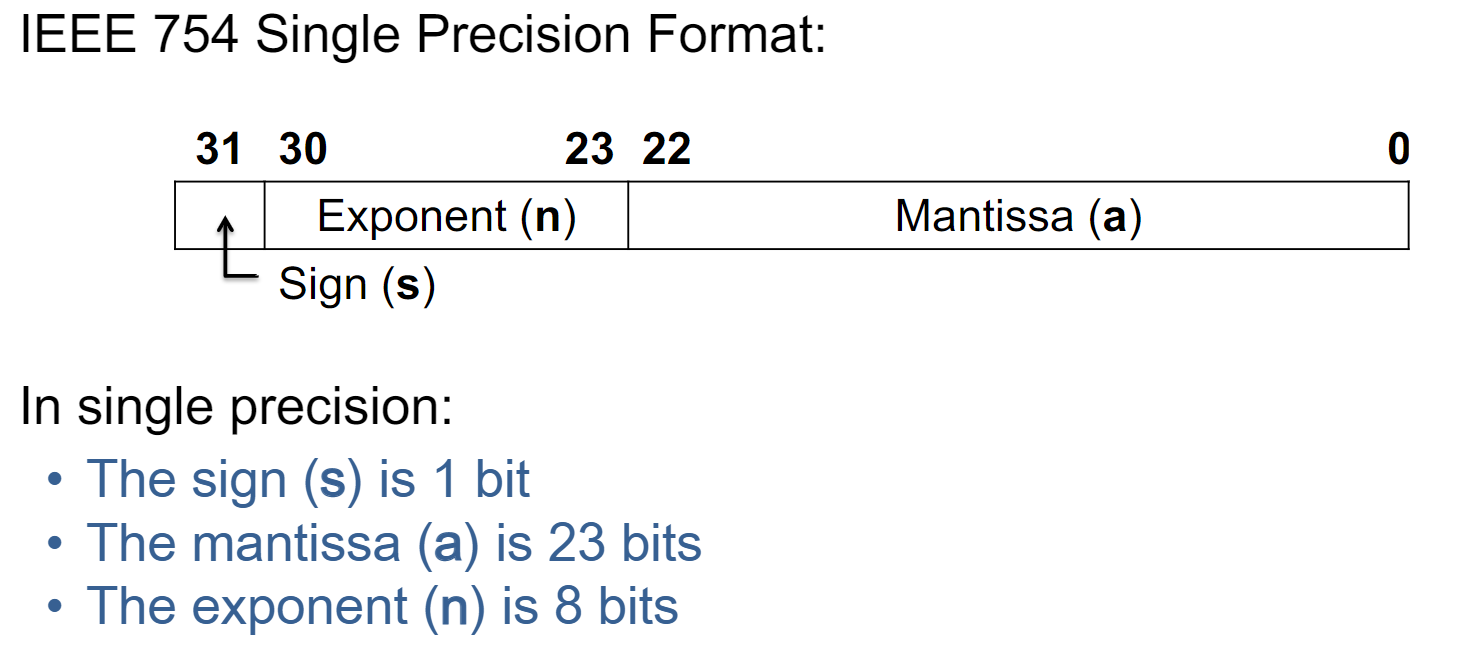

IEEE754 standard