ELEC271 W1-2

本博客草草创建,简陋不堪。本人才疏学浅,笔记也不过给诸君作一参考。如有疑惑/错漏/建议 还请使用这个匿名提问箱,我会一一回复。 不过现在本博客也增加了评论功能,你也可以直接在底下说。不过这个评论功能没有提醒……回复可能会不够及时。

https://www.tapechat.net/uu/5r0pL8/ZV9H0543

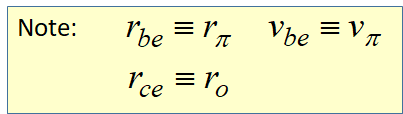

WEEK1: Transistor models

我的评价是:如果忘光光了,可以看看我的EEE109笔记: EEE109 笔记补档 (https://luobutan.com/categories/EEE109/)

概览:

由来:

原理:

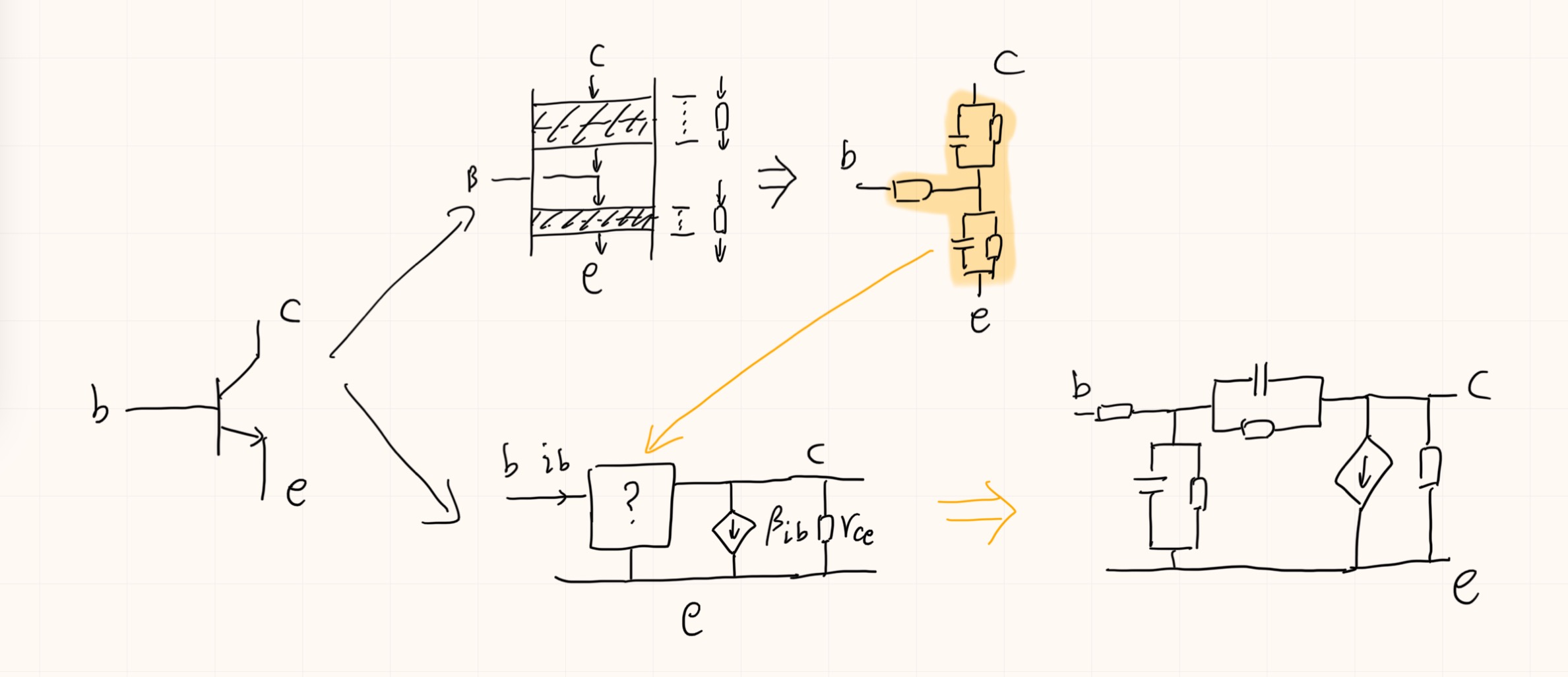

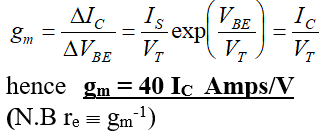

二极管有一个pn结,三极管有两个。由于两个厚度不一样产生了不对称,也就有了BCE三极。

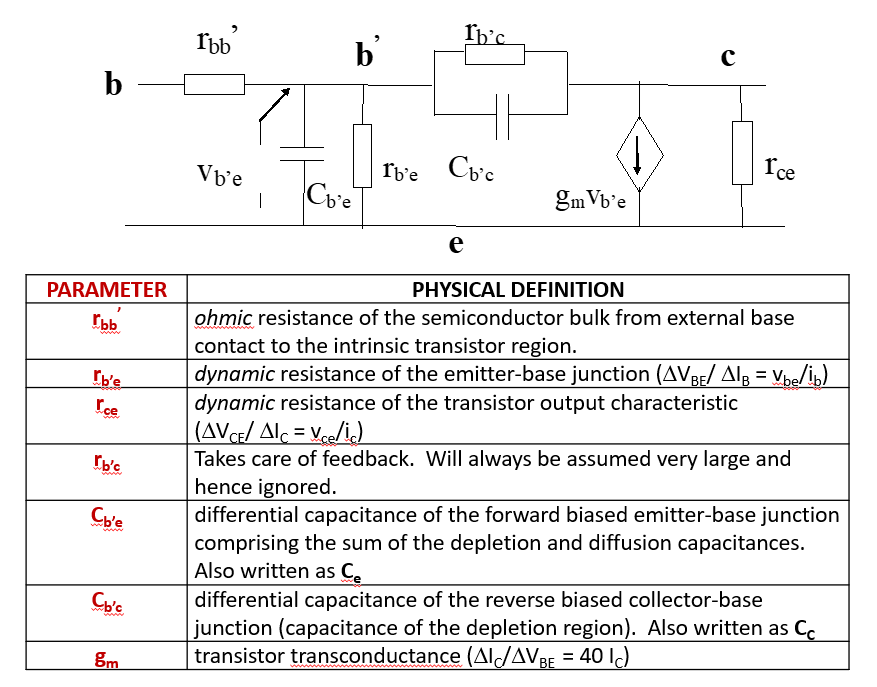

在我们所学的混合π等效电路里,rb'e,Cb'e,rb'c,Cb'c都是对这两个pn结的模拟——pn结本质上就是一个电容,但同时电流可以通过它所以还有电阻。

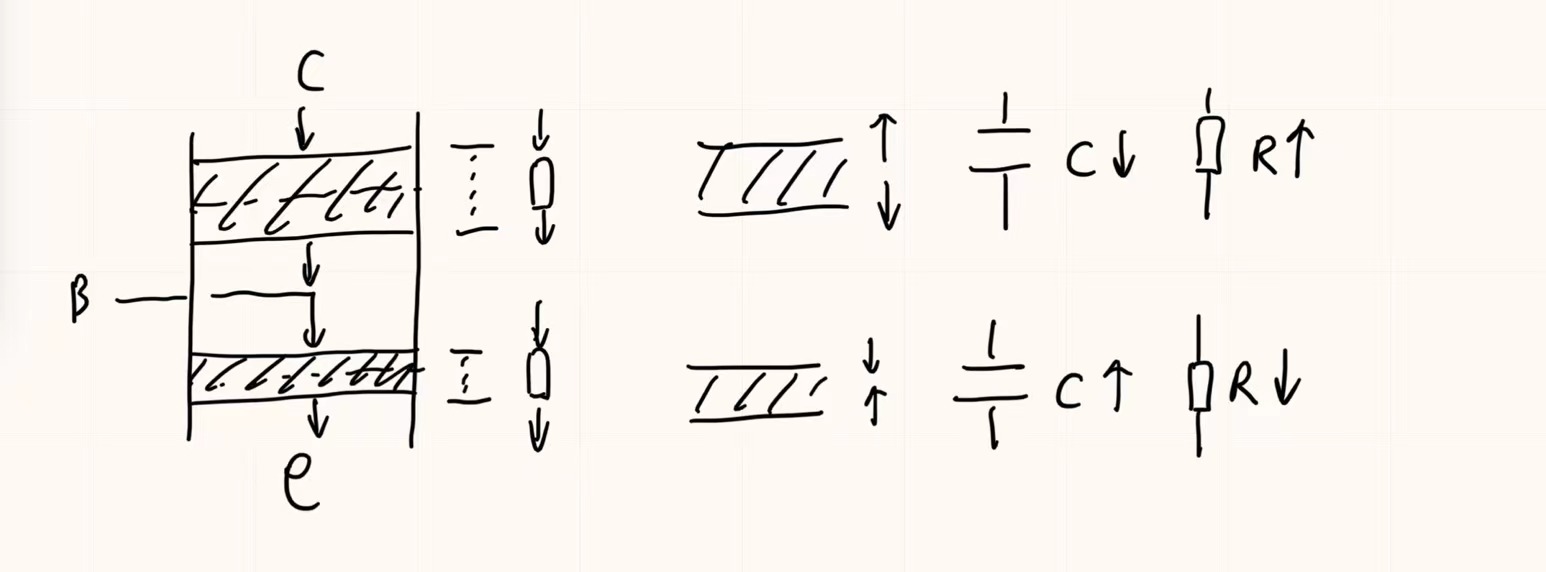

那么,pn结越宽,相当于电容两个极板间的距离被拉大,电容就越小。而电流要通过的耗尽区变宽了,于是电阻就增大:

因此,对于更厚的bc端pn结,rb'c更大,Cb'c更小。因为Zc=1/2πfC, 电容越小阻抗越大,因此对于BC端,无论是电阻还是电容的阻抗都更大,所以在更粗略的近似里我们常常直接把bc这两个全都视做断路。

| parts | more | How |

|---|---|---|

| rbb' | 从基级接口到pn结的基级半导体本身的欧姆电阻。在低电流水平下与电流大小无关。 | |

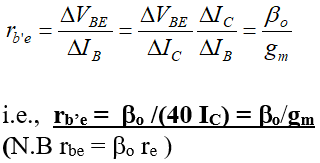

| rb'e |  |

B-E pn结在交流电下的动态电阻 |

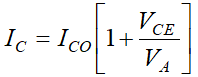

| rce |   |

三极管的输出动态电阻 |

| rb'c | 非常大,当他断路 | |

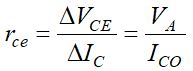

| Cb'e |  |

B-E pn结在交流电下的动态电容。该结在三极管工作时是正向导通的所以同时包含势垒和扩散电容 (相加即可,不做展开。) |

| Cb'c | C-B pn结在交流电下的动态电容。该结在三极管工作时是反向截止的所以只考虑势垒电容,相对Cb'e来说较小,但之后频率响应会有讨论。 | |

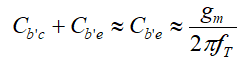

| gm |  |

三极管跨导 |

WEEK2: Transistor amplifier

Transistor amplifier 是基于三极管设计的放大电路,基本上分为4种:

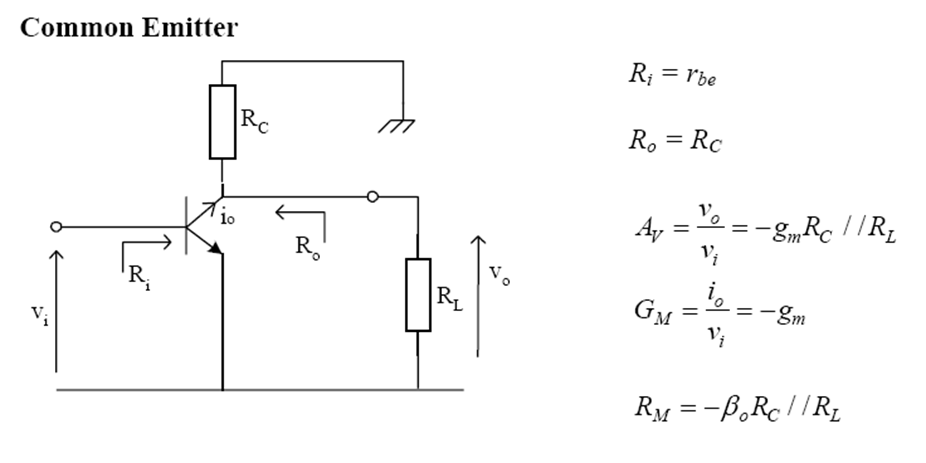

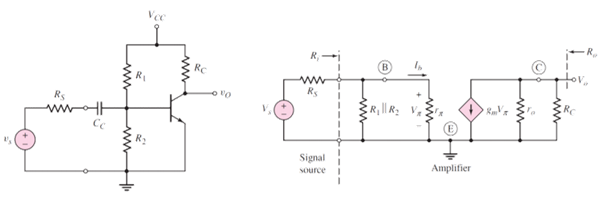

- Common emitter (CE) 共发射极

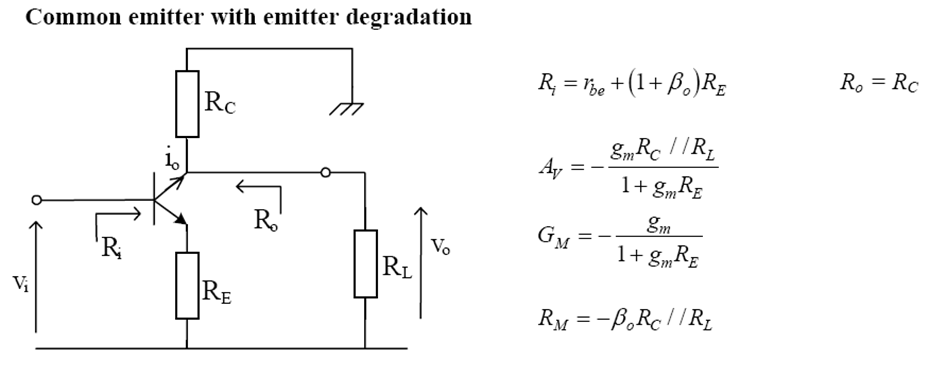

- Common emitter with emitter degradation (CE-ED) 退化共发射极

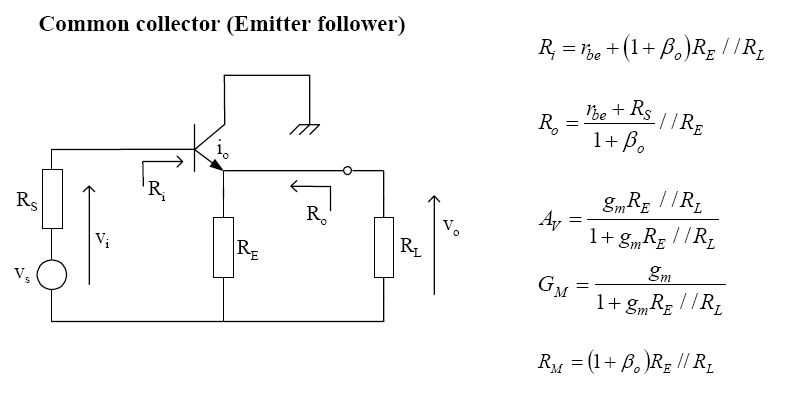

- Common collector (CC) also known as emitter follower (EF) 共集电极/射极跟随器

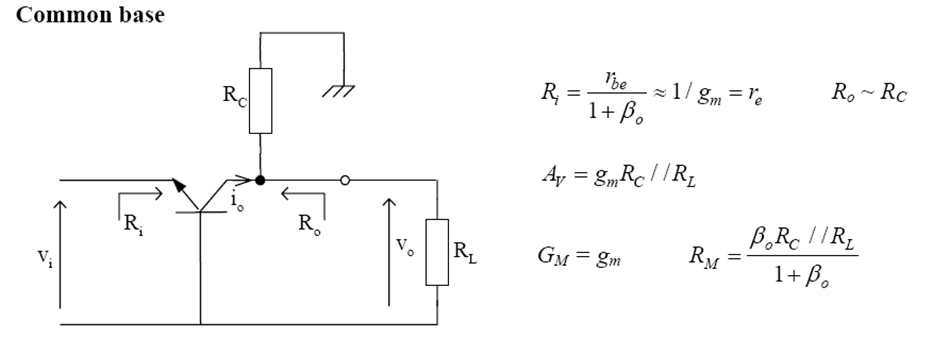

- Common base (CB) 共基极

| Property | AV | AI | Rin | Rout | Usage |

|---|---|---|---|---|---|

| CE | high | high | Medium | high | Most useful, general purpose |

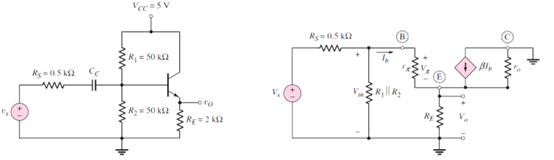

| CE-ED | Low | high | high | high | \(R_E\) constitutes feedback – sacrifice \(A_V\) for increased stability: less dependent on \(\beta_0\) (also temperature), increase Rin |

| CC(EF) | Low (< 1) | high | high | low | Impedance matching – high R-source to low-R load (also very linear – used in power amp. Output stages) |

| CB | high | low (<1) | low | high | Impedance matching – low R-source to high-R load (also features in Diff.Amp. – see later notes) |

Common Emitter (CE) 共发射极

Common Emitter with emitter degradation (CE-ED) 退化共发射极

Common Collector (CC) / Emitter Follower (EF) 共集电极/射极跟随器

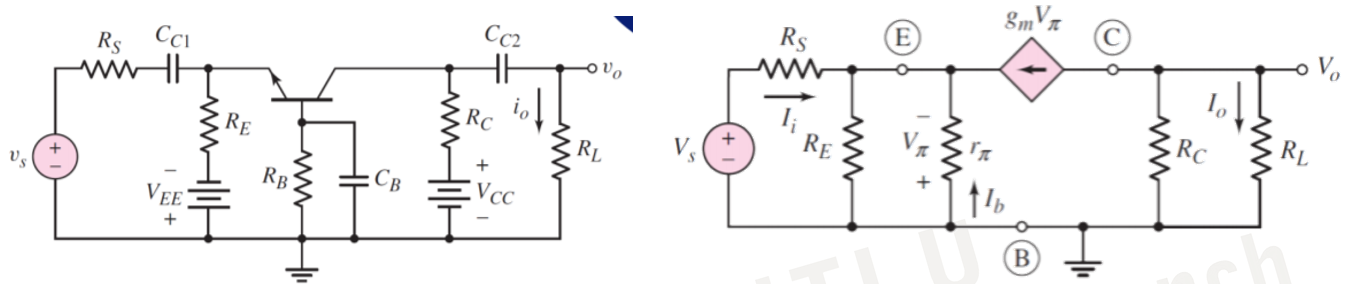

Common Base (CB) 共基极

WEEK2 Addition: Bootstrapping

在目前的讨论中,我们所有的放大或缩小对象都是电压,所以如果把我们搭建的电路看作一个amplifier,那么我们在讨论的一直是voltage amplifier。而对于一个理想的voltage amplifier,input resistance将会是无穷大,因此我们设计的input resistance越大越好。

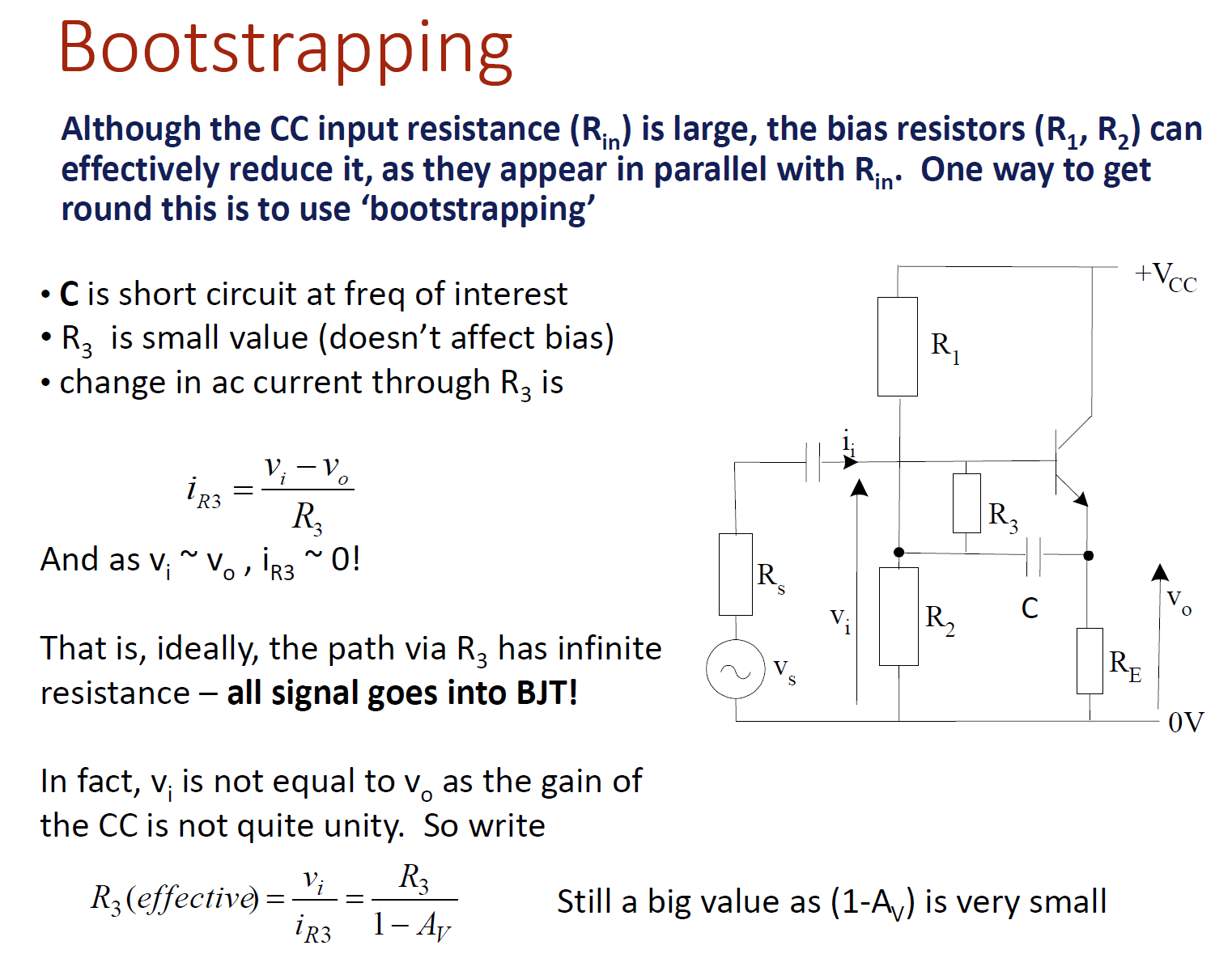

然而,比如在common collector中,用于确定直流偏置的两个电阻在交流等效电路里是并联的,因此input resistance被大大减小了。这个时候,我们就要用到bootstrapping:

bootstrapping其实就是对原来交流信号直接接入两个电阻对中间做了手脚,加了一个大电阻R3和一个电容。

对于直流信号,电容断路,因此直流偏置电压不变。而对于交流信号电容断路,所有的信号全部返回至输出端。而在此基础之上,大电阻R3在交流等效电路中和原来的输入电阻串联,避免了信号对直流偏置点的干扰又增加了输入电阻。具体计算如图。

值得注意的是,(我个人认为)bootstrapping电路向我们初步展示了在各类模拟电路里进行计算的原则:我们写出某个点的电压/电流表达式,或者某两个点电压/电流的比值,然后将它们和某2点之间较为简单的电路方程作联立,并最终得出结论。和我们的直觉相比,结论可能会有点奇怪,或者有些反直觉,所以我们可以再将最终式子的每一部分返回去电路去做比较,找出相应的物理意义,这样我们才能最终理解了整个电路。